- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

average in FPGA or RT

03-24-2011 02:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all, I am very new to this Labview. I currently trying to measure voltage in the NI 9205. I went through the tutorial in the data logging to disk Link and i kinda build my application based on that. I want to take the average of some samples every so long. For exmple, i want to average 1 second of data every 20 seconds. I read through some of the posts that it mentioned some code that can be used. However, i am not sure where should i put the averaging. Would that be in the FPGA vi or the RT vi?? My logic told me that it should be at the FPGA vi b/c then i only need to pass data that i want to the FIFO and to the RT. However, i tried a few of them and none of them work.

Also, i used the DO channel on the 9205 to activiate a power supply which is needed for the measurement. Should that be in the FPGA vi or the RT vi. I have attached the pic of the vi i had here.

Thanks in advance for the help.

03-24-2011 02:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

With reference to DO channel can it drive the power supply? Or and you energising the power supply via another relay system?

You FPGA code does not take acount of any delay in the initialisationof the power supply. Also you appear to be turning it on before you execute

and turning it on again after execution. Your FPGA code is sampling 2 channels.

Yet your RT code is logging 4 channels. Suggest you modify you RT code to a producer consumer architecture!

Log to your file in consumer loop.

In this simple case i would do the averaging on the RT.

xseadog

03-28-2011 12:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That was my work in progress shot. Yes, I used a relay circuit to trigger the power supply with the DO channel. I have attached the following pictures with the setup that i had. I tried to connect mean.vi and it said there is an error with the type of data. How could i convert the data??

What i am trying to do here is before the measurement, allow 3 sec to turn on the power supply and achieve a stable voltage, then read data for 1 sec to the FIFO. Then on the RT side, average out the 1 sec of data and write it to the tdms file. Is this the proper way to do it??

Thanks again for the help.

03-29-2011 08:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can someone help me with this issue?? I am kinda stuck with this issue now.

03-29-2011 01:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

One issue I see is on the FPGA VI.

The second frame of the flat sequence, this frame will get one sample of data from each channel, write it to the FIFO and just sit and wait for 1 second. (Yes the timer is actually in parallel, but the idea is the same.)

What you want it to do is loop for 1 second: read a sample, write it to FIFO, repeat.

Well the issue is that card can sample at 250k samples/second, 4us per sample (1 channel). If you are reading 6 channels it will take 24us to sample all six, yielding ~42000 samples of data, 6 channels wide. On the Real-Time side you need to configure the FIFO to have enough room to store all the data. Then you can read and average.

For 6 channels you would need to loop 250000/6 = 41667 times.

Do you need to sample that fast?

How many samples do you need for that 1 second interval?

If it is less than ~120k you can use a shift register as an accumulator and just have the RT host divide the final count by the sample number.

03-29-2011 02:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For some reason I couldn't edit my previous post.

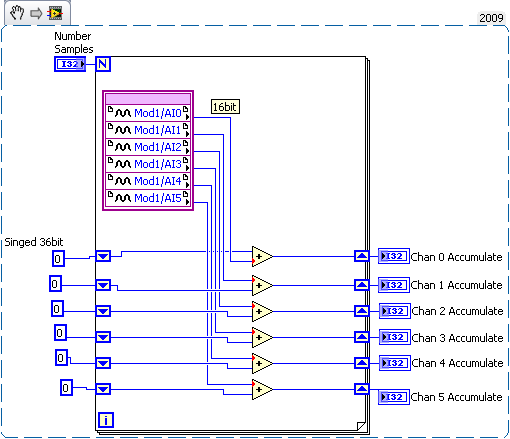

Here is a quick lashup of what I was thinking:

Couple of points: The module is set in raw format to save accumulator space. On the RT side one would need to convert from raw counts to a meaningful voltage. The number of samples in this example is limited to 65536 before a roll over is possible to occur. On the RT side I would divide the "Chan x Accumulate" by the "Number Samples" to get the average value.

03-29-2011 02:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the reply. One question that i have is I need to use FPGA target because I need to use the digital output to trigger the relay for the power supply and turn it off after reading. So i need to do this in the FPGA target.

For now i only have 6 channels but ultimately will be around 30 channels. I am just trying to get the software going.

I will try to fix up the FPGA vi first and make sure it is reading probably.

03-29-2011 03:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have updated the FPGA vi and it is shown below.

03-29-2011 03:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have tried different number of "Number of Elements" in the FIFO output it doesn't work. If i put in 250,000 as number of elements, it gives me error. If i put in 0, then it got a few lines of 0. If i put in 6, then i only got 1 line of elements.

Any FIFO FPGA expert??