- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Variable reluctance sensor signal simulation

Solved!07-06-2020 12:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Developers,

I recently started working on a project to simulate several sensor signals, it is a Hardware In the Loop testing system, I need to simulate a variable reluctance speed sensor signal, the signal is a sinusoidal with 24 pulses per revolution, one pulse has a lower amplitude than the other 23 pulses, I found in other old post a VI which generate a sine wave that is multiply but a square wave with a duty cycle calculated based on the number of missing teeth, so while square amplitude is zero sine is multiplied by zero and We get the pattern for a crank shaft sensor, instead of that the signal I need has one pulse with a lower amplitude, any idea on how I can do this, maybe generating a sine wave counting zero crossing and every 24 pulse multiply sine amplitude to have one pulse lower than the other 23??? I am pretty new using labview HIL suite and the PXI system with RTOS and FPGA module, any info or help will be appreciated. Thanks

Solved! Go to Solution.

07-06-2020 10:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Usually there are two input variables , position and speed, both have an influence on your reluctance sensor output.

One possible FPGA approach: First look-up table for position to du/dv value , followed by a multiplication with speed.

Henrik

LV since v3.1

“ground” is a convenient fantasy

'˙˙˙˙uıɐƃɐ lɐıp puɐ °06 ǝuoɥd ɹnoʎ uɹnʇ ǝsɐǝld 'ʎɹɐuıƃɐɯı sı pǝlɐıp ǝʌɐɥ noʎ ɹǝqɯnu ǝɥʇ'

07-06-2020 10:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

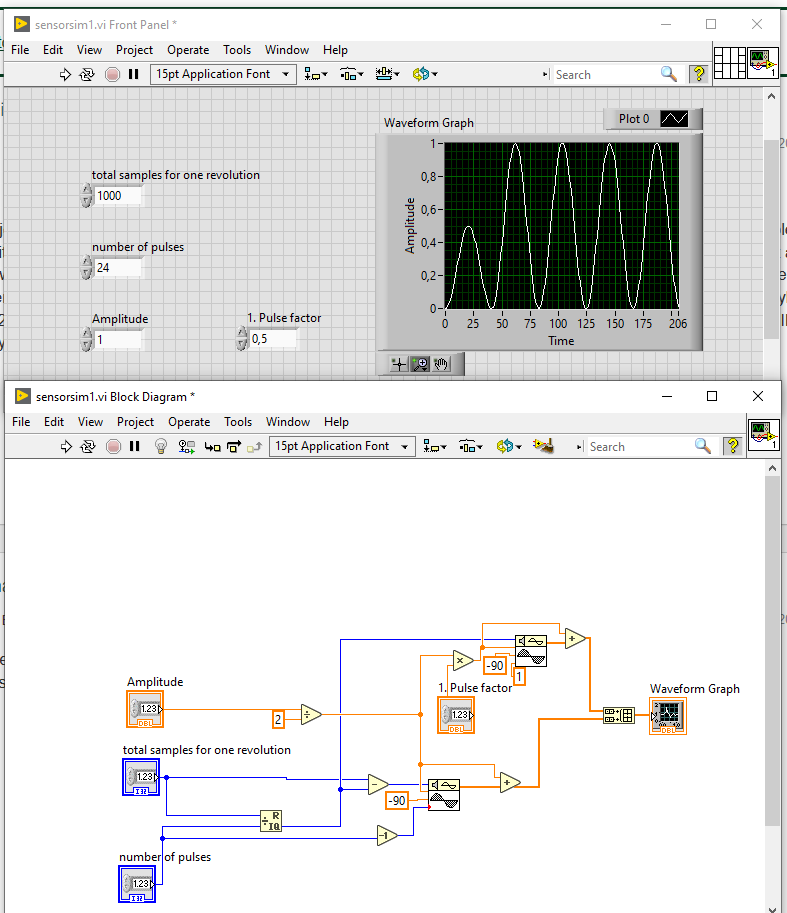

here is one quick solution for a simple 'simulation' ..

edit : the vi posted creates two versions since I don't know how your signal looks like. maybe a starting point, shown is just one ..

Henrik

LV since v3.1

“ground” is a convenient fantasy

'˙˙˙˙uıɐƃɐ lɐıp puɐ °06 ǝuoɥd ɹnoʎ uɹnʇ ǝsɐǝld 'ʎɹɐuıƃɐɯı sı pǝlɐıp ǝʌɐɥ noʎ ɹǝqɯnu ǝɥʇ'

07-06-2020 07:49 PM - edited 07-06-2020 08:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

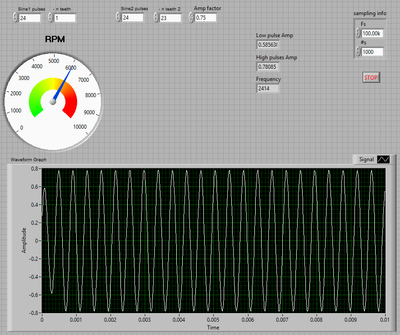

Hi Henrik, thank you so much for your help, based on the VI you shared and a VI I found in an older post from 2005, I developed a new VI that generates the signal I need, signal has 24 pulses per revolution, 1 pulse has a lower amplitude than the other 23 pulses, It has a linear behavior for the amplitude respect to RPMs, I attached the VI I generated and the VI I found in addition to the one You shared. Any comment or idea to create a more efficient VI will be appreciated. Also an image of the signal generated below. Thanks again.