- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Tons of "noise" and zeroing out in FPGA data

01-28-2019 07:14 PM - edited 01-28-2019 07:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

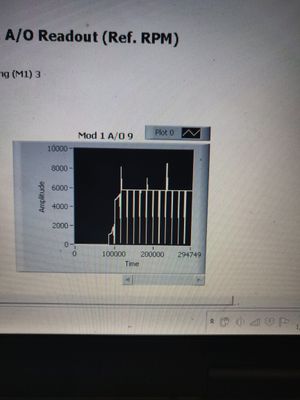

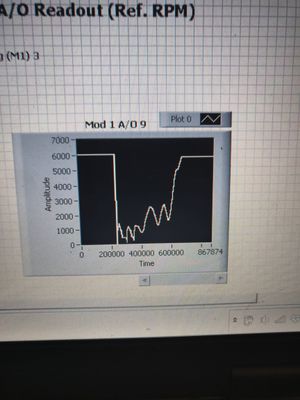

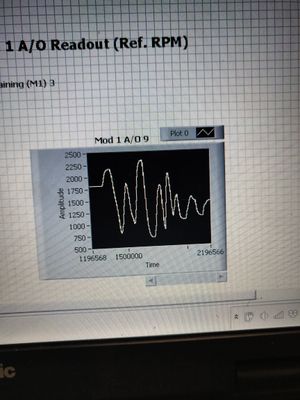

I'm acquiring RPM data on a cRio 9014 with the 9118 chassis, with an NI 9201. Eventually we will collect 5 pieces of data, RPM, Speed, Torque, Voltage and Current all connected to the NI 9201. Something interesting is happening when we're trying to collect RPM data.

What could be causing this?

01-28-2019 08:15 PM - edited 01-28-2019 08:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here is something odd I see.

In your FPGA you have a timeout control that is set to 5, and you write that to the timeout value of the FIFO Write.

But in your host code, you have a write to that timeout control, but the value in the control is defaulted to zero. Are you changing that before you start the VI? So when that is passed to your FPGA before the loop starts, a zero would get written to the FIFO Write timeout.

It seems like that might cause problems.

01-29-2019 08:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yeah that does cause problems if not set correctly. It's measured in uSec but I've just been lazy and haven't set the default

01-29-2019 09:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Are you sure it's not clock ticks? 1 clock tick is 1 usec on a 1 MHz clock. But many of my FPGA's are on a 40 MHz clock.

01-29-2019 10:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Wait yeah you're right it is in clock ticks. Our FPGA is also on a 40 MHz clock. So is 1 clock tick still 1 usec here, or is 40 clock ticks 1 usec?

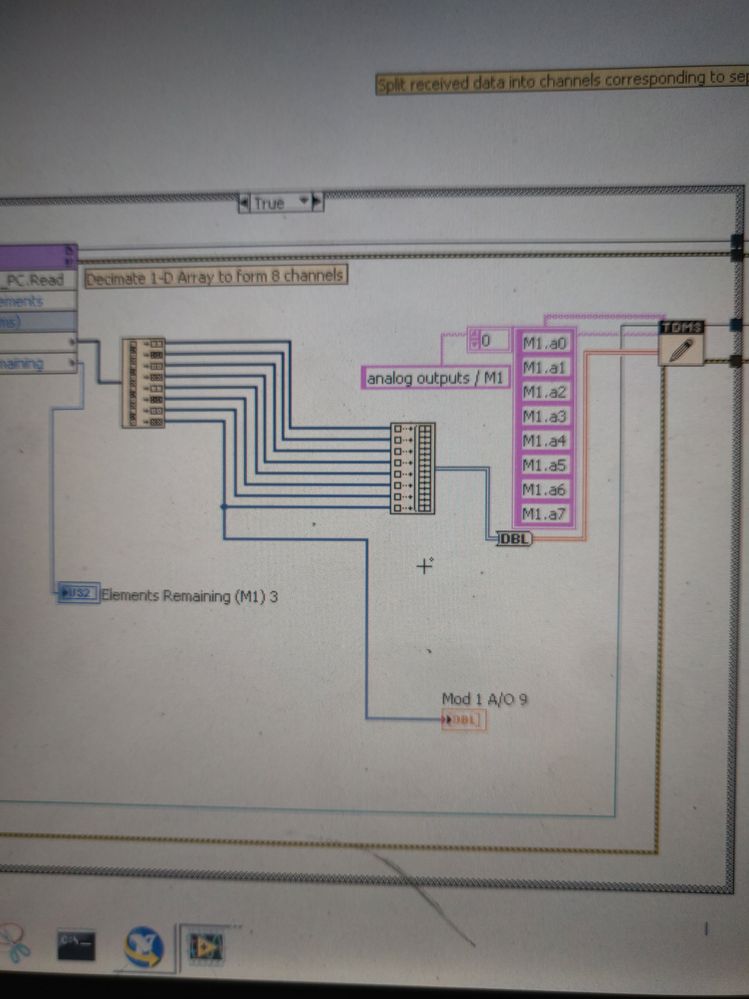

also, something interesting, when I disconnect all the other analog inputs right before the TDMS file write method, the program works a lot better.

01-29-2019 10:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Correct. 40 clock ticks would be 1 usec on the 40 MHz clock.

01-29-2019 10:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

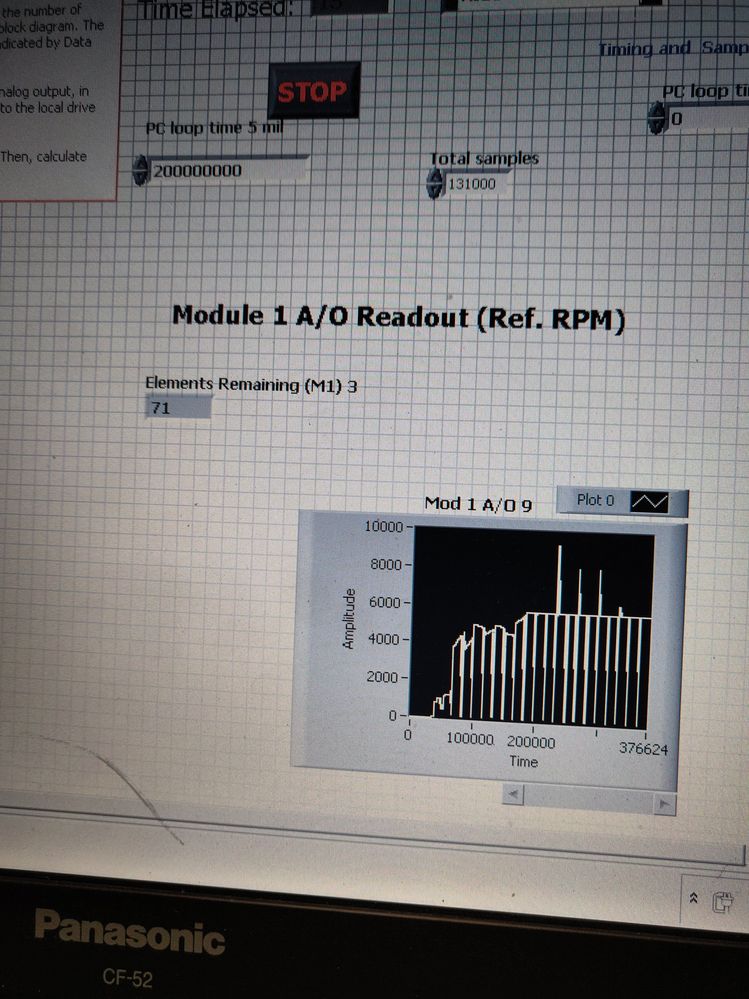

so for timeout control, for 5 sec, i would have 200000000 clock ticks. Just tried that and while it's a little cleaner, we're still getting ups downs and etc. Did I do the math correctly? anything else that could be the problem?

01-29-2019 11:29 AM - edited 01-29-2019 11:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Since I wasnt the one who wrote the original program I'm still a little lost as to what the timeout control is supposed to be. It's "5" in the .vi that goes into the FPGA, that's 5 clock ticks and not 5 seconds right? So, isnt the host vi also supposed to be "5"?

I also tried compiling no timeout on the FPGA side and, like expected that didnt do much other than stop recording data in 2 seconds.