Hi all,

I'm working in an LV cRIO FPGA application to generate PWM/Pulses on multiple output channels my code consists on a state machind controlled by different input variables (bool, fxp). The software is working for 1 channel and i decided to convert to subVI so i just have to call a subVI fro each output channel (from the Top-Level).

Here the software doesnt work anymore. I have read in the forum that the standart variables are just sent when the subVI is called and then updated when the subVI finishes (like a function call in C programming) and that the solution is to use global variables. Is there any other way to do it more hardware-like? I mean that the variables are updated in the Top-Level, are also updated inside the subVI, (without using global variables.) I'd be grateful if you can point me some example.

Thank You!

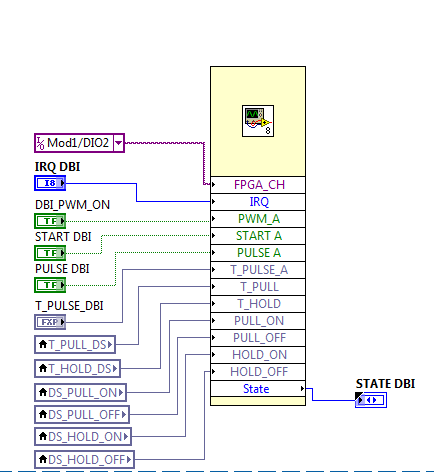

subVi call

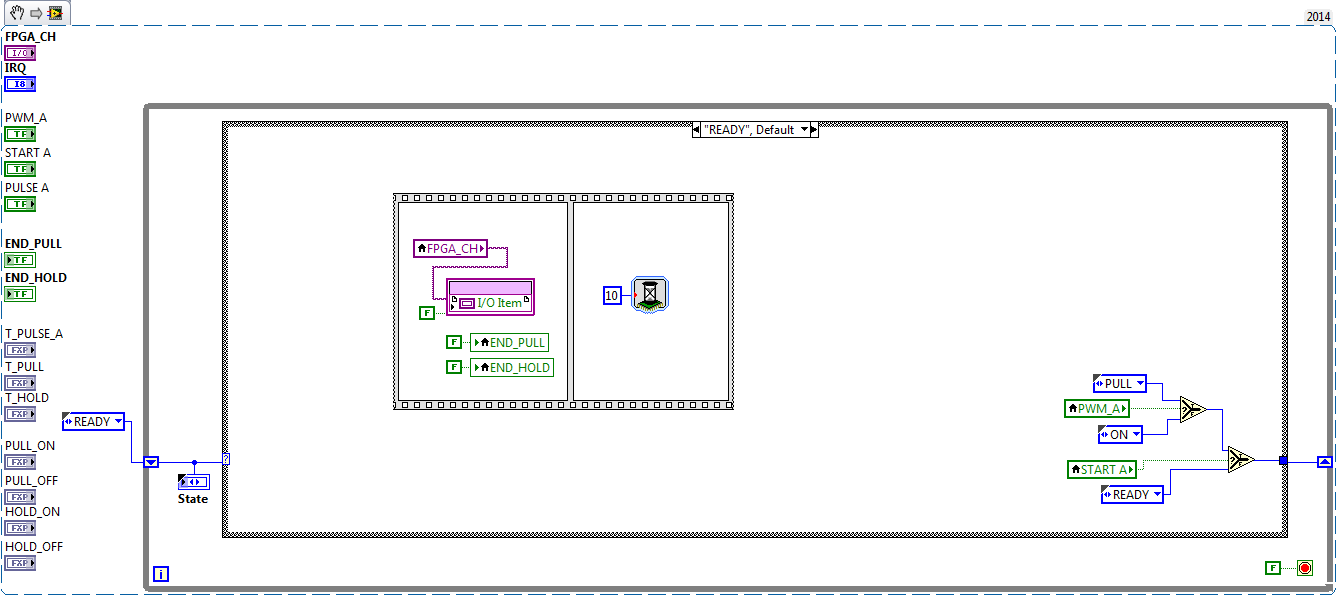

subVI code

subVI code