- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Spikes in signal when change the clock type of SCTL

05-17-2021 02:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

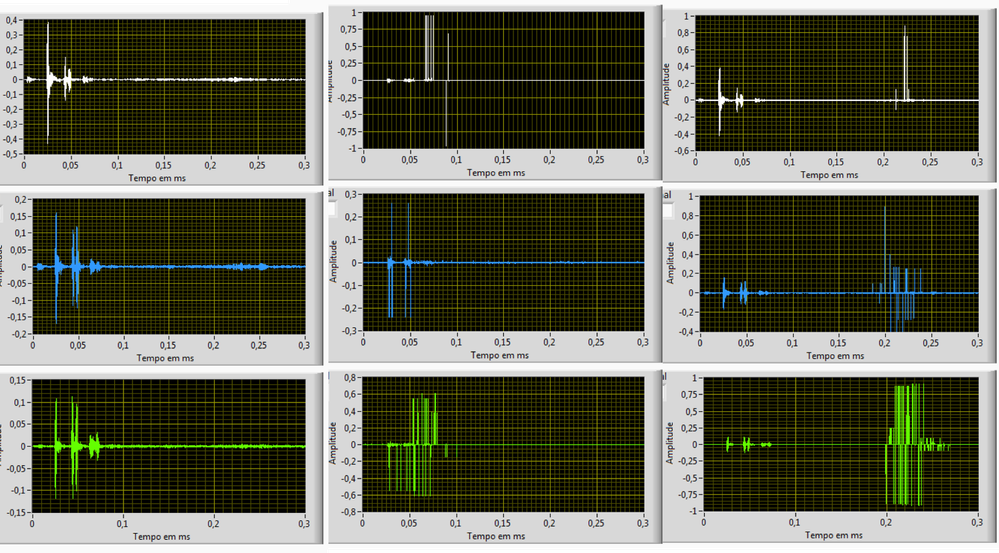

I have a FlexRio 7962 (with NI-5752 adapter) capturing a waveform generated by an AWG (NI-5412). In the FPGA side, when I set the clock of my SCTL as the "40MHz onboard clock" or any derived clock, the signal presents some aleatory spikes (Figure). I already measured the signal directly with an osciloscopic and it does not happens.

Otherwise, when I set an external clock (IO Module Clock), It does not have spikes but presents a considerable time delay.

Would anyone have any ideas?

05-18-2021 10:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, as described in NI 5752 CLIP documentation, all its ADCs are clocked by IO Module Clock 0. Therefore, accessing I/O node of ADC data should be inside of SCTL clocked by IO Module Clock 0.

https://zone.ni.com/reference/en-XX/help/372614J-01/friodig/5752_clip_help/

05-18-2021 11:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, the I/O node of ADC data already is inside of SCTL. But, when I set the clock as "IO Module Clock 0" (connected to the AWG by a SMB cable), the collected data coming with a considerable and aleatory time delay (wrong measurements). And, when I set the clock as any derived clock (in the Figure is 20MHz), the data has no time delay but presents these spikes.

So, I have 2 problems:

Clock = IO module clock 0 - (time delay)

Clock = 40MHz onboard or derived - (correct time measurement, but has spikes in the signal)