- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Some Problems When Using LaBVIEW to Call Veristand

Solved!06-26-2017 09:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am aiming to use LaBVIEW to do some automative test ,which needs call Veristand from LabVIEW pannels.

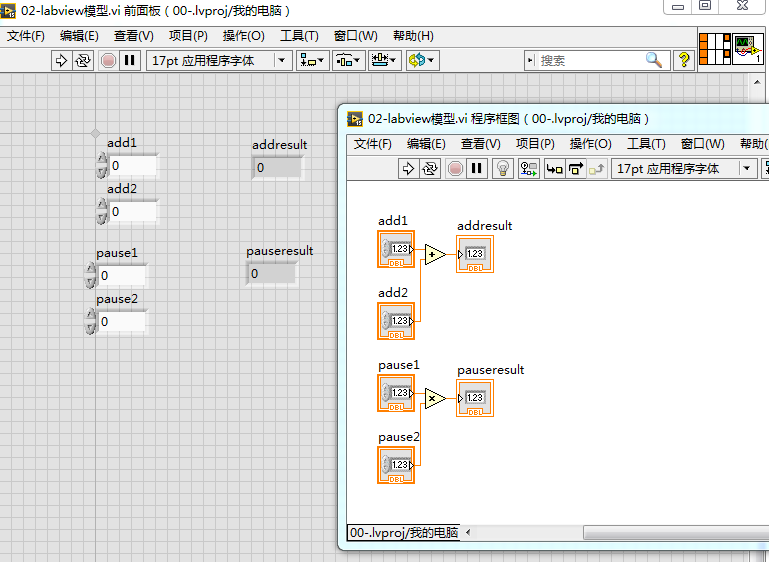

First, I need a LV-model to run in Veristand, below is the code:

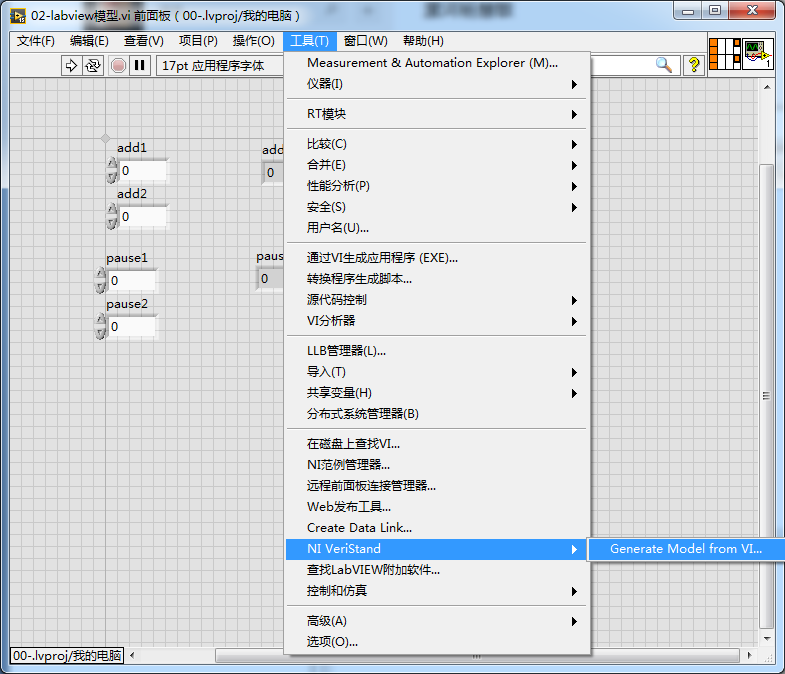

then I use the menu function to translate it into a LV-model(all by default settings ),see as below:

Then I got the model.

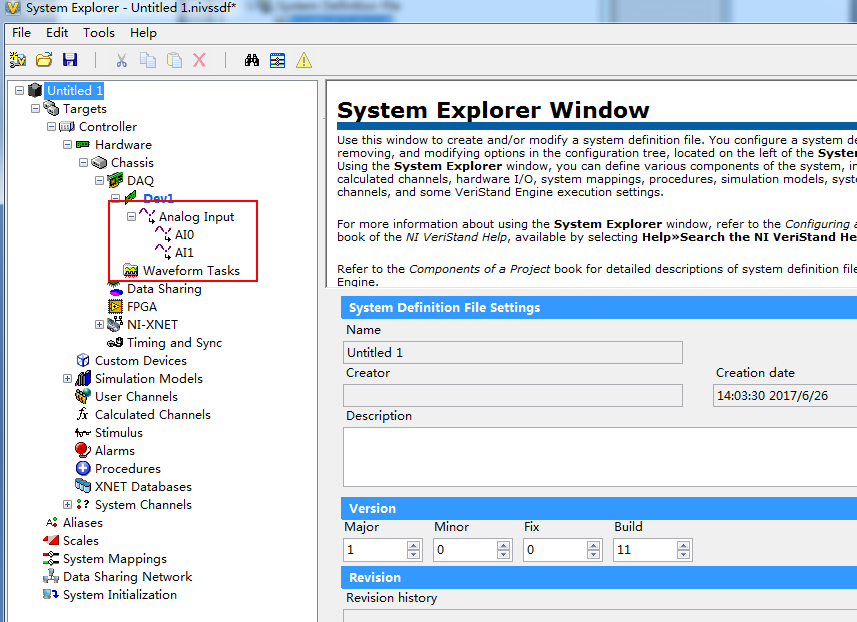

I created a virtual device PCI-6230 by MAX,and imported it in veristand,see as below:

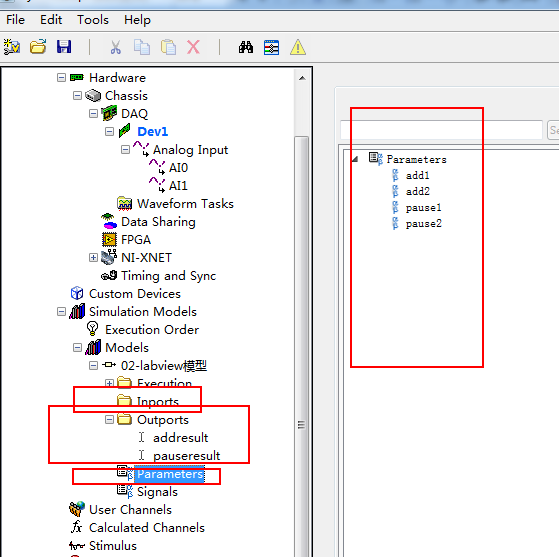

I imported the model,

This seems a little beyond my expection ,What I want is "add1""add2""pause1""pause2"appear in "Inports",but they dropped in "parameters". I searched Veristand Help, and find the instructions:

I suspect NI just regards the necessary inports as "Inports", otherwise they will be treated as parameters. How can I make them as "Inports"?

Then I need to map them. I opened the mapping pannel,see as below:

This thoroughoutly puzzled me,because I can not connect the voltage value with the model's input(or parameter), the left list and the right list are not same, and something does not appear.

I want run the project ,and set the control the value 'add1' and 'add2' by MAX(set the channel value),and get the value 'addresult' by LaBVIEW.What shall I do ?

Solved! Go to Solution.

06-27-2017 12:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You already found the solution, but did not understood that, 😛 When assigning the connector pane in LabVIEW, you can right click on the connector and select that as "required" ( This is a basic step shown in core 1 training ). Do this step before generating the model.

06-27-2017 04:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thank you ,it really works ,thank you

06-27-2017 05:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please mark it as solved.

06-27-2017 07:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

06-27-2017 10:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The Left list is source list, and the Right list is destination list. Sources are supposed to be mapped on to the destination. One source can map onto many destination, but One destination can have only one source associated with it.

Source : It is basically the data source, which is having it's own data, Ex: Analog Input, Model Output, Serial In data, file read data.... these all takes data from outside and bring inside the veristand boundary. (I'm considering that whatever computation happening inside the model is unknown to the veristand, and seems as a black box)

Destination : The generation channels Ex: Analog output, Model Input, Serial Output, File write.... These all takes out the data from veristand boundary to the outside world.

For a simple application, you may map your analog input to Model Input, then Model output to analog output. Note that, in both the case source are mapped to destination.

Note: in this list in veristand the destinations are also listed in the source list, this may look little confusing, but the fact is, the destinations can also behave like a source when it is mapped to any source. in such case, the actual source's data will be used.

06-28-2017 04:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thank you, thank you, you are really a nuibility