- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SBRio-9651 Dev Kit Internal Pullup for Onboard Switches and LEDs

11-18-2020 01:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

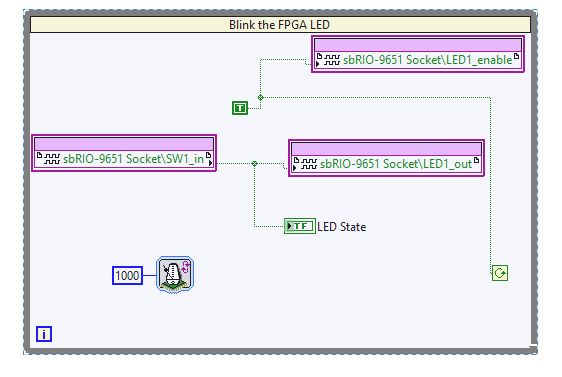

Hello, I'm a new Labview user messing around with the SBRio-9651 Dev Kit, I made a simple program to turn on the onboard LED when I press the push button underneath it (LED1 and SW1 from the DevKit3 CLIP). I'm trying to change either of these signals to use the internal pulldown and swap the logic without changing the HDL. When I modify the CLIP using the NI CLIP Generator tool (and observe the change in the resulting XDC file) the running program does not change behavior. Can someone please help me out with this? I have not worked with FPGAs in sometime so it might be a fundamental understanding I am missing.

Thanks!

Dan

XDC snippet:

# DIO_31

#################################################################

set_property IOSTANDARD LVCMOS33 [get_ports {aDio[31]}]

set_property SLEW Fast [get_ports {aDio[31]}]

set_property DRIVE 8 [get_ports {aDio[31]}]

set_property PULLDOWN true [get_ports {aDio[31]}]Basic Program:

11-19-2020 05:25 AM - edited 11-19-2020 05:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Why do you think an internal pulldown resistor would change anything in the logic of the user switches or LEDs?

The sbRIO-9651 development board already has an external pulldown resistor of 4.7kOhm on the user push buttons 1 and 2. For the DIO_31 which drives the USER_LED1, a pulldown makes absolutely no sense since it is an output. The pulldown at best could define the logic level as long as the output is disabled, which in your VI you consequently enable anyways. Once the output driver is activated it will override whatever pulldown or pullup you could possibly select.

11-19-2020 09:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your answer. As I said I'm fairly new to FPGA's so a lot of my understandings are rudimentary. I figured the reason could be a larger external resistance on the inputs. As for the LED, forgive me if I'm entirely wrong on this, but I thought that making an output pin set to PULLDOWN would make it an "active low" output signal, hence driving a voltage through the output pin in its idle state and bringing it down to ~0v when activated. Is there a different way to perform this as pin attributes and not within the logic?

Again thank you

11-20-2020 04:53 AM - edited 11-20-2020 04:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This is basic electrotechnique and not specific for FPGA's at all. A pull down or pull up resistor defines the signal level when the input or output is inactive, nothing more and nothing less. If it would be strong enough to override the actual function of the device driving the input or the output driver, then it would be basically short circuiting that driver and nothing good can come from that.

But can you explain to me why you do not want to define such an inverting functionality inside the FPGA logic that drives the output pin? That is what the FPGA logic is meant for so why try to invent a fantasy functionality that never will work since it is against physics, when you can simply drop a boolean inverting node inside your loop?