- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Real-Time: issue reading FIFO from FPGA

12-15-2011 02:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Everyone,

I've found that I'm unable to read from a "target to host" DMA FIFO at the rate I need. I suspect there are ways to speed this up, so if anyone has any tips I'd appreciate it.

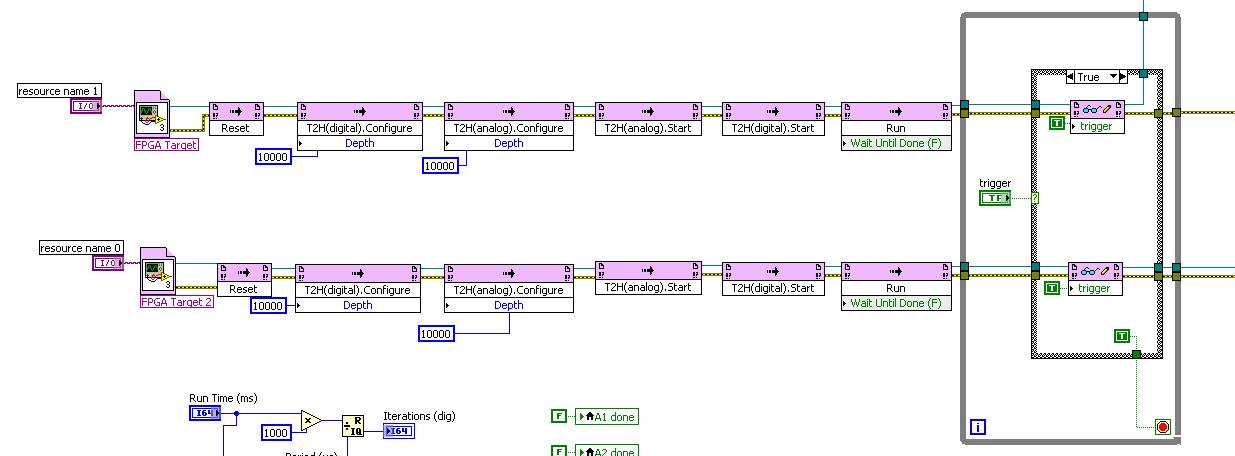

I'm attempting to read 96 digital inputs from an FPGA target (PXI 7825-R) using DMA transfer to a Real Time host (PXIe-8133). On the FPGA target I am writing the 96 bits as 3 U32's, which are written consecutively inside an SCTL running at 5MHz. 3 elements * 5MHz = 15 M elements / sec. Everything seems to be going well on the FPGA side of things.

On the RT host, I am reading 10,000 elements in each iteration of a timed loop. Thus I need this loop to run at a rate greater than 1.5KHz in order to keep up with the rate the FPGA is writing at. (10000 elements * 1.5KHz = 15 M elements / s)

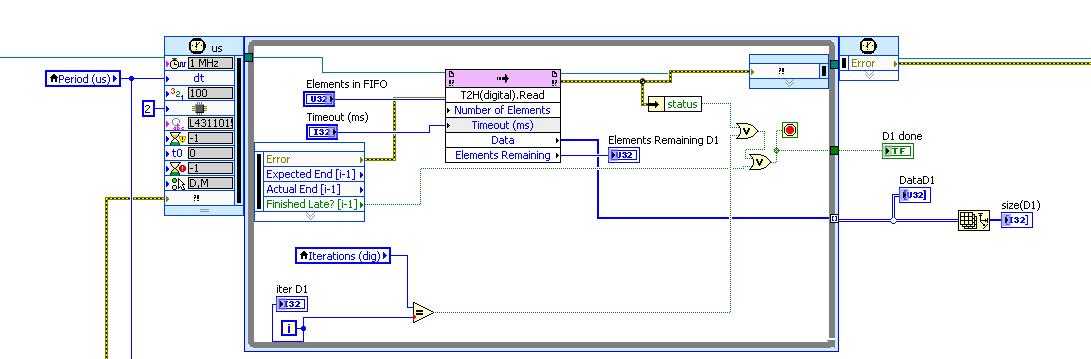

Unfortunately, my timed loop on the RT host times out if I set it to run at faster than 0.5 KHz. Testing has shown that the limiting factor is the rate at which the FIFO.read can read the 10,000 elements. I've tried running with fewer elements per read and a higher loop rate, but no combination made a significant difference in the overall rate of elements / sec. I realize that I have some variables and indicators in the loop that could be removed to make it run faster, but I found that stripping the loop down to the bare bones of just the FIFO.read and the stop criteria still didn't achieve a much faster loop rate.

I've added images of the relevant components of my VI's below. Any help is much appreciated. Also, if anyone notices anything else wrong with what I'm doing, please let me know as well.

Thanks alot!

JP

FIFO read loop on RT host

Configuration and start up of FPGA and FIFO on the RT

DMA write loop on the FPGA

12-16-2011 02:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

JP,

1. What is your Timeout(ms) set to in your T2H(digital).Read on your RT host vi?

2. A general rule of thumb that I, and some of my colleagues, use when configuring FIFOs is to set the depth of the FIFO 10x bigger than the expected number of elements.

3. Where exactly, or how exactly, are you determining that your RT VI is timing out?

National Instruments

12-16-2011 04:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Larry,

1. The timeout is set to -1 on the RT vi. I had tried setting it to 0, but that caused to read function to timeout right away and produce an error.

2. Thanks for the tip, I'll do that.

3. When I say the read loop on the RT vi is timing out, what I meant is that the "finished late" out put on the timed loop becomes true, indicating that the contents of the loop take longer to execute than the time I set for the loop.

Thanks for any help you can offer.

Justin

12-16-2011 05:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Justin,

Since you have a -1 wired in for your current timeout of your FIFO Read, this means that the read will wait indefinitely until there are [Elements in FIFO] available to be read. It is very possible that the reason that your timed loop is finishing late is because the FIFO Read is waiting indefinitely for there to be [Elements in FIFO] available before it tries to read and your timed loop is set to execute faster than the FIFO write is providing the number you set for [Elements in FIFO].

One approach you can try to test this theory is by adding a timeout value to your FIFO Read. This way, you can find out if the FIFO is not filling up fast enough to be read based on the number of elements it is expecting to read. Since your timed loop finishes late if you set the rate to be faster than .5kHz(or 2ms), I have some suggested combinations for you to try, and you're also willing to try your own values:

Loop rate: .5kHz - Timeout for FIFO Read: 2ms

Loop rate: .5kHz - Timeout for FIFO Read: 3ms

Loop rate: .5kHz - Timeout for FIFO Read: 1ms

National Instruments

12-19-2011 03:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Larry,

I tried what you suggested. Running at 0.5kHz and timeout=1ms caused error 50400, which I believe is accosiated with the fifo.read timing out due to not filling in the alotted time.

Running at 0.5kHz with timeout = 2ms or greater worked without error.

It seems that the implications of this are that the FPGA code is only writing elements at roughly 10,000/2ms or 5M elements/s. I thought that based on my FPGA code, it should be writing 3 elements each cycle in a 5MHz loop, for a rate of 15M elements/s. Looking at my FPGA code (posted originally), do you see anything wrong with that structure, any reason why it would not be behaving as I expect?

Please let me know if my understanding of this result is correct. Thanks for your continued advice.

JP

12-19-2011 03:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ah, yes I see that sequence structures are not to be used in an SCTL.

So teh first of ym 3 FIFO.writes executes, and the otehr two can't, since they are attampting to execute simultaneously.

So I need to figure out a clever way to sequentially write to the FIFO 3 times, since I can't fit all the data in at once.

12-19-2011 05:26 PM - edited 12-19-2011 05:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What LabVIEW Version are you using? I believe as of 2010 you can bundle these three data words together in a bundle / cluster and write the cluster to the FIFO as a single element. Then just unbundle them on the receive end. I believe you may have to save the cluster as a type def but thats not really an issue. I have used this successfully in the past.

EDIT

Ignore that! It seems this is only for transferring data round in the FPGA, not target to host. I remember I had to interleave as is suggested below

Craig

12-19-2011 05:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

03-14-2013 03:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thak you that is nice, but what if I want to use an SCTL plus interleaving? After all, that is one reason to use FPGA at all.

I cannot place a foor loop into an SCTL. The sequence may be placed , but will be removed when compiling, according to the manual.

Any ideas? In the meantime I will try to find a way....

03-14-2013 05:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Set your loop feequency to 20MHz on FPGA.

Wire up a FXP +2,2 to an increment +1 and a shift register to generate a counter 0,1,2,3,0,1,2,3,0 and so on.

Use this to run a mini state machine on the FPGA with

State 0 : Read the DIO ports and put them in a shift register

State 1 : Write DMA 1

State 2 : Write DMA 2

State 3 : Write DMA 3

Shane.

PS Another option is to make the main loop run at 15MHz and put the correct DIO read and DMA write in a state machine which has only three states.