- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Questions about FPGA Derived Clock

Solved!04-05-2021 09:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Hope you are doing good,

I need to implement SPI protocol on FPGA that requires clock periods of 13ns (~76Mhz) to synchronize data. Hardware in use: sbIRO-9638 with default clock period of 25ns (40Mhz).

I tired using derived clock of 76.923076923077 MHz under derived clock option, it gives a value of 13ns period and message shows "Valid Configuration". I can compile something as simple as incremental counter but when attempted to compile something complex (attached example code) it fails because of timing violation "Timing missed by ~3.9ns". It seems like complexity vs execution speed issue.

Same code (attached) gets compiled when using a derived clock of 80 &100 Mhz. Is this because ~76Mhz is an odd frequency to achieve and the way clock is divided? I do know what piece of information I am missing here and how it is actually working.

I have read several articles and tried different solutions available online, such as using case structure to reduce down clock from a higher frequency, optimizing code etc. At this point I am fairly convinced that it is on possible to achieve what I am expecting.

My questions are:

1) Is it possible to achieve ~76 Mhz frequency on this board and execute a larger code?

2) Should I somehow make the code more efficient?

3) If not, does NI has a board that can support this frequency?

I appreciate your time.

Thank you.

Solved! Go to Solution.

04-06-2021 08:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This article does say that if "If the FPGA target does not support FPGA-derived clocks or the FPGA base clock you add, the New FPGA...."

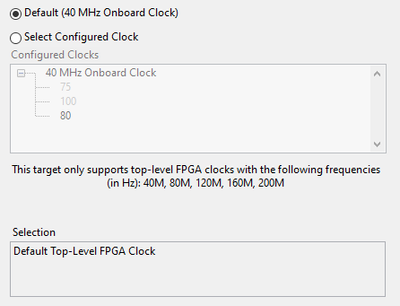

Which it does, if I try to select 76 Mhz or 100 Mhz clock as a top level clock both options would be dimmed. Since "This target only supports top-level FPGA clocks with the following frequencies (in Hz): 40M, 80M, 120M, 160M, 200M"

Still hoping if there is ANY possibility of getting a 76Mhz clock or should I accept this as a limitation?

04-06-2021 08:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I think there is no way you can get 76..... MHz.

The derived clocks come from the base clock rate further subdivided to 2x, 3x, 4x, 5x. It must be an integer. You can't get a clock that requires a fractional multiplier of the base clock.

04-06-2021 09:21 AM - edited 04-06-2021 09:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi RavensFan,

I really appreciate your reply!! This helps a ton!

One more question, this would be out of LabView's scope:

Do you think that this statement will stand true mainly because of the clock (40Mhz) used on this board? Say, hypothetically, a custom board is created using 1000Mhz clock (crystal oscillator) then in that case a closer to expected frequency can be achieved, correct?

04-06-2021 09:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well. If you had a 1000 MHz base clock (1 ns period), then you could get a 13 ns period which occur every 13 clock ticks. It would be like a clock divisor as opposed to a clock multiplier.

04-06-2021 04:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi RavensFan,

Once again thank you for responding to my basic questions. I did some more reading and I think I better understand the workings of FPGA clock now.

A bit bumped knowing that I cannot implement this protocol on this FPGA though. 😓

Have a good day!

04-06-2021 07:18 PM - edited 04-06-2021 07:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It looks like some NI FPGA targets support an external clock for running SCTL's, but I can't find a list (ugh). I *think* the FlexRIO line supports it?

Also, what exactly are you doing with the data? Could you acquire or generate it via DAQmx or something? Those frequently support external clocks, and you could interface with the FPGA via the RTOS. Your delay would be much longer than directly in the FPGA but it might not matter for your application.

Also, I believe NI has some pre-generated FPGA IP that'll do SPI but I couldn't find it in a quick glance. Edit: Try this https://forums.ni.com/t5/Examples-and-IP-for-Software/SPI-IP/ta-p/3491325

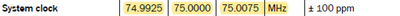

Also also, do you have to hit 76 MHz *exactly*? Usually SPI devices have a tolerance range they can operate in, maybe you can make 80 MHz work?

04-07-2021 11:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi BertMcMahan,

Thank you for your response,

Firstly, they do provide IP-Core which can be implemented to an FPGA that meets their requirement. Requirement being having a clock period of 13ns or 75Mhz. Which is why I first asked if that is even possible.I mentioned 76.9...Mhz value as an example since it gives a clock period of 13ns.

Second, I am new to this so do not know much. But I will try to explain the most I can. From my understanding so far this protocol is not a straight forward implementation of SPI protocol as it uses only two wires and sends data using transreciever IC. What appears like is data is created as SPI, converted and then sent out using transreciever IC.

It looks like some NI FPGA targets support an external clock for running SCTL's, but I can't find a list (ugh). I *think* the FlexRIO line supports it

For now, as far as the hardware goes, I have to stick to sbRIO-9638. But it is good to know, I will look into it to see if we can use it.

Also, what exactly are you doing with the data? Could you acquire or generate it via DAQmx or something? Those frequently support external clocks, and you could interface with the FPGA via the RTOS. Your delay would be much longer than directly in the FPGA but it might not matter for your application.

Since I could not implement the IP (also I do not have it yet) assuming it will not work given the clock period limitation, I have been desperately trying to recreate the master signals sent to the slave (Shortcut). Just to see if I can get some response but these signals comes out in a certain sequence generated using some logic. What it appears like is this data over transreciever IC is supposed to be captured, get converted into SPI data, go through a synchronization process, interpret and send next master signal out as required.

I have only worked with FPGAs so far I do not know how exactly I can approach this task using DAQmx. But I will read about it.

Also also, do you have to hit 76 MHz *exactly*? Usually SPI devices have a tolerance range they can operate in, maybe you can make 80 MHz work?

I cannot say for sure but their tolerance range is a bit tight:

If it is okay with you, can I send you a direct message providing more details? I cannot share all the details at the forum.

Thank you for your time.

04-07-2021 12:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@XM43 wrote:

If it is okay with you, can I send you a direct message providing more details? I cannot share all the details at the forum.

Unfortunately this basically exhausts my knowledge of LV FPGA external clocks, so you'll have to find someone else more familiar with it. I'm basically just guessing now as well, sorry. Good luck with your project.

04-07-2021 12:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

oh okay.

I really appreciate your input. Thank you