From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

12-17-2020 04:18 PM

I have an FPGA at 40MHz and I'm performing an FFT in a single-cycle timed loop with an FFT size of 8192 and it is set to Single Channel, Single Sample. Does this mean one point is outputted every clock cycle? So since every clock cycle is 25ns, one FFT takes 25ns*8192 = 205us?

Solved! Go to Solution.

12-17-2020 04:33 PM

When you configure the FFT Express VI it has a setting for throughput, you want to select 1 sample per cycle to run at the clock rate. Default is not 1 sample per cycle (I think it is slower).

12-17-2020 06:50 PM

Yes, I have it set to 1 cycle/input for Throughput. So that means one data point is processed and outputted every clock cycle?

12-17-2020 07:15 PM

Yes, it should take 8192 cycles.

After configuring it, hover over the function. It should also give you latency figures as well; cycles where you have no outputs.

12-17-2020 07:57 PM

I see, and it says the latency is 20534 cycles. Does that mean it goes 20534 cycles without producing an output?

12-17-2020 08:31 PM - edited 12-17-2020 09:27 PM

@Trekkie123 wrote:

I see, and it says the latency is 20534 cycles. Does that mean it goes 20534 cycles without producing an output?

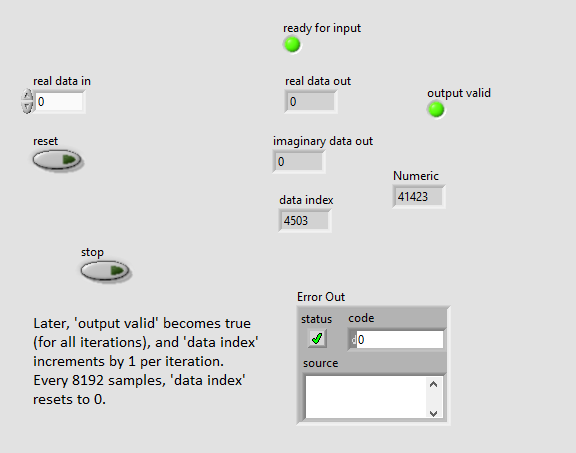

Yes - latency in this case is the number of cycles you have to wait in order to get valid data. But since you have 1 cycle/sample, you should get 20534 cycles of not-valid data, then cycles #20534, 20535, 20536... are all valid data.

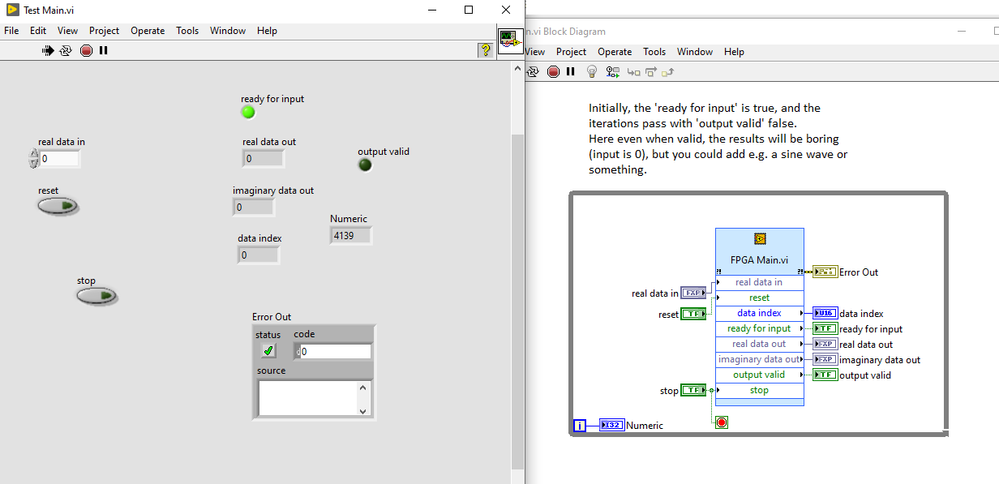

Attached is a project that uses the Desktop Execution Node to demonstrate this (LabVIEW 2019, with a cRIO-9045 in the project, no hardware required).

Below are a couple of images with 0 inputs. I modified the project after to use a sine + random value to get a marginally more interesting output...