- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with the Labview FPGA Compile Cloud Service

Solved!05-06-2018 01:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

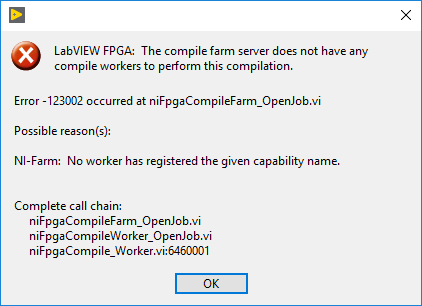

I'm having problems to compile my FPGA code using the FPGA compile Cloud service. I had done it on Friday without any problem, it was always working and the only change I did in the VI was to change the default value for a control. Starting from this Saturday I got this error message

I have an ASL license from my university. I went to my account on the browser and my license is ok.

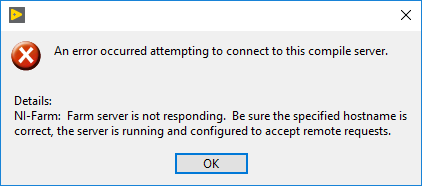

Even more, starting from this Sunday I even couldn't reach the server. Only using a VPN service the connection is established. Otherwise, I'm getting the next error

I live in Russia, and we are having a lot of services blocked last time. I really hope that nobody is blocking the service, I really need it.

I turned off my firewall. I tried with my wifi connection at home. I wait for one day, but the error is still there. I thought it can be a problem related to the server, but I didn't see any other post related to this issue on the forum.

I'm attaching the code. but I suppose it won't really help.

Thank you for the help!

Solved! Go to Solution.

05-06-2018 11:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I get the same error with your project here in Australia (no registered capability), so it seems you're not being blocked.

Using a local FPGA compile server (which includes Xilinx 10.1, Xilinx 14.4, Xilinx 14.7, Vivado 2013.4, Vivado 2014.4 and Vivado 2015.4), your project compiles successfully using the Xilinx 14.7 compiler (I've attached the bitfile if that helps). So the cloud server must be misconfigured or in some strange state. It might be worth raising a support ticket with NI to try get it resolved. In the meantime can you setup a local FPGA compile server? Here's a link to various compile tools if you don't have them already.

Unless otherwise stated, all code snippets and examples provided

by me are "as is", and are free to use and modify without attribution.

05-07-2018 12:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, Michael!

The bitfile is much useful! And in the meantime, I will be installing Vivado. I understand that Xilinx is not compatible with windows 10, isn't it?

05-07-2018 01:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Glad the bitfile helped. The compile server I used was running on Windows 10, though it does sometimes throw errors with certain compilations (the compile worker just crashes). Technically none of the FPGA compile servers are supported under Windows 10, but they still seem to work well enough.

You'll need the Xilinx (ISE) 14.7 compiler, as that supports the sbRIO model you're using. The version I have is from LabVIEW 2015 SP1. It sounds like later LV2016 FPGA and later can not be installed under Windows 8/10.

Unless otherwise stated, all code snippets and examples provided

by me are "as is", and are free to use and modify without attribution.

05-07-2018 02:06 AM - edited 05-07-2018 02:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have the same problem this morning in Switzerland.

Compiling locally..... yawn.

This is going to cripple my throughput today.....

05-07-2018 08:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Bump.

OK, the week has definitely started in the USA by now, I was hoping the compile servers would be functional again by now.......

Please fix this, it's utterly destroying my productivity.

05-07-2018 09:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

We are currently seeing the behavior internally and are making the proper teams aware of the issue. Unsure of the cause as of right now. We are hoping to have this resolved shortly.

Applications Engineering

National Instruments

http://www.ni.com/en-us/support.html

05-07-2018 09:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you. ![]()

05-07-2018 09:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Seems to be working again. Hopefully it stays that way

05-07-2018 10:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for reporting this issue. The problem should be resolved.

Sorry for the inconvenience.

William Hackett

National Instruments