- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Peer to Peer Streaming Data

Solved!07-23-2018 06:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

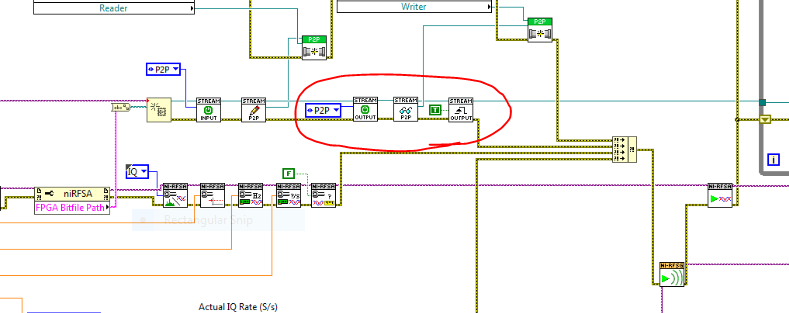

I am new to Labview and I have been trying to set up a peer to peer connection between the Vector Signal Transceiver PXIe-5646R and the FlexRIO PXIe-7976R. Using the NI Streaming Host Example provided by NI, I am able to send data to the FPGA board, but the data does not match the inputs. I am not sure what the problem is. Any help? I attached the main code, the FPGA code, and a screenshot of the output.

Thank you,

Serg

Solved! Go to Solution.

07-24-2018 05:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Serg,

I'm not familiar with how the example is set up initially, but I can see in the code that you're processing the data before sending back to the host. If you simplify the code to only acquire samples with the VST and stream them to the FlexRIO, do you still see issues with the data? Maybe you could perform a finite acquisition and ensure that the streamed samples match those returned by the RFSA session, this way we could narrow down this issue to something related to the program or the hardware configuration.

Jon F.

Technical Support Engineer

National Instruments

07-25-2018 01:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jon,

I modified the code to acquire and stream the data to the FPGA board, and I am not getting anything across. Furthermore, the RFSA is not acquiring the correct data from the RFSG. If I remove the peer to peer communication code, the RFSG and RFSA work properly. Attached is the new code and the output.

Thank you,

Serg

07-26-2018 02:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Serg,

Did you make your FPGA code from scratch? I opened the example and it calls out a specific bitfile for the FlexRIO. Were you able to find the FPGA code for that bitfile?

I'm curious if there is an issue with unpacking and packing the data on the FlexRIO FPGA. If we can find the source code for the default bitfile that would be something easy to check.

I'm unsure if you should be able to return the data from the RFSA session after setting up a p2p stream...

Jon F.

Technical Support Engineer

National Instruments

07-26-2018 04:43 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Jon,

My FPGA code is a copy of the original FPGA code. The only difference is the element and IQ data indicator that I added so that I could see the data the FPGA board was receiving.

Attached is the original example as it was delivered to me.

I can remove the RFSA code. I just wanted to make sure that the RFSA was receiving the correct signal before sending it to the FPGA.

Serg

07-27-2018 11:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Serg,

I got the chance to take a deeper look into this and I think I have some input about what is going on here. By default, the example is configured to take the signal at VST RF IN, stream this to the FlexRIO, perform a frequency shift, then stream the data to the RFSG(VST RF OUT) session to output.

From looking at your code, it appears that you'd like to generate a specific signal from RF OUT, acquire this through RFSA session, and stream this data to the FlexRIO for processing (please correct me if I'm wrong). The way your code is set up, the data you write to the RFSG session does not affect what it is outputting. That is why by default the example mentions writing 'dummy data' to the RFSG session--it will never actually be output. It only outputs a frequency shifted version of what you acquire with RFSA.

If what I said above is correct, you will want to remove the parts of the code that are streaming to the RFSG session.

If you remove the parts that are configuring a stream to the RFSG session you should see the correct data.

Jon F.

Technical Support Engineer

National Instruments

07-30-2018 03:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jon,

You are right. I want to generate signals using the RFSG and send them to the RFSA through the RF OUT and RF IN ports. From the RFSA, I wish to send them to the FPGA board for processing and eventually to the host. After removing all reference of an output stream, I still don't get the correct inputs signals out of the FPGA board. At one point, I removed the processing blocks from the FPGA code, but no data ever reached the FPGA.

Serg

07-31-2018 12:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you seen this example code:

http://www.ni.com/example/31398/en/

This implements something closer to your application--it may provide some insight into how to configure everything properly.

Jon F.

Technical Support Engineer

National Instruments

07-31-2018 06:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jon,

I took a look at the example and was able to modify the code to make it work with my equipment, I can now get a signal from the RFSA to the FPGA board. This example is better than the one I was using.

Thank you,

Serg