- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PID (FPGA) - Convert 16bit output to 24 bit

12-07-2009 12:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

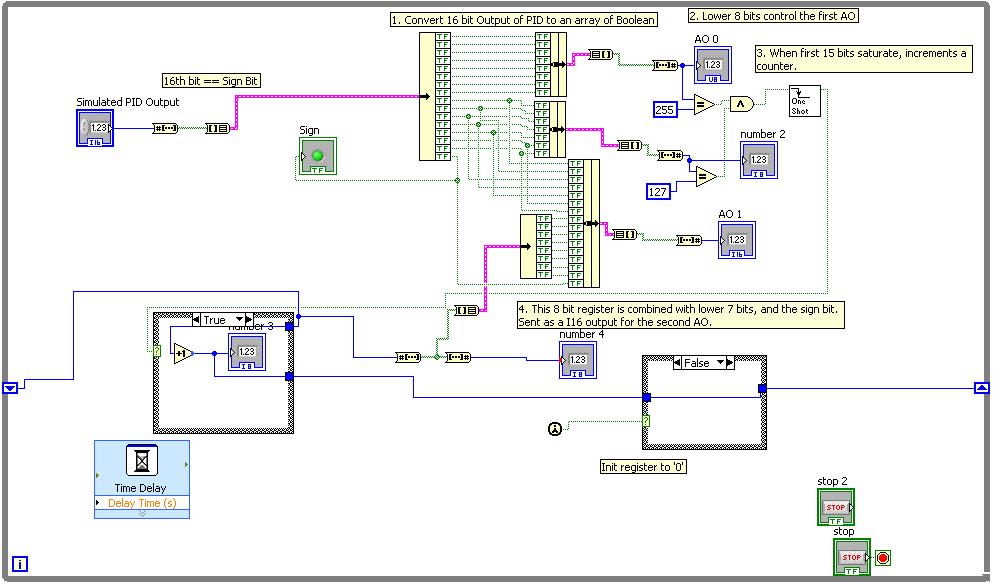

Im controlling a device in Closed Loop using the PID (FPGA) vi. The output of this is I16, but it would be nice if I could convert it to a I24, or I32. The output of this vi is sent to two different Analog Outs on my Op-Amp circuitry. The op-amps are set up as summing amps, so it would be ideal to send the lower 8 bits to the first AO (fine output), and the top 16 (15+sign) to the second AO (coarse output).

I haven't found an easy way to do this yet. So far, I've been thinking of just using the I16 output value, split it into two 8 bit numbers. The lower 8 bit controls my first AO. The upper 8 bits is combined with another 8 bit register that gets incremented everytime the 8-bit number becomes saturated, and controls the 2nd AO.

I've attached a pic to make it more clear (I hope?). If I should be doing this another way, please let me know.

Or maybe I need to be controlling this system with 2 parrallel PIDs? One controlling the coarse control, the other the fine. The feedback would be the same for both PIDs.

12-07-2009 01:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Actually, nevermind for now. Im just going to manually control the upper 8 bits of the coarse control. This way, there will be no 'jumps' when incrementing the upper 8 bits.

Thanks!

12-07-2009 01:52 PM - edited 12-07-2009 01:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi bones,

even on FPGA you should be able to use "split numbers" and "join numbers" functions...

And you can use boolean operators on numbers. Like sign = I16 && 0x8000 ![]()

That way you would get away from all those number TO boolean array TO cluster of booleans TO unbundle TO bundle TO boolean array TO number conversions (also called RubeGoldberg, search for this in the forum!).