Hi,

I am trying to communicate my PC with my cRIO-9034 via RS422. To do so, I have a NI9871 module in my cRIO.

One of the communication lines runs at 4800bps, and works well.

I need to use the second port of the NI9871 to read messages coming from the PC. Those messages are 4208-bytes length each, and the PC sends a message every 80ms. The baudrate of the communication line is 921600bps. The line has only two wires, which go from PC (TX+, TX-) to the NI9871(RX+, RX-).

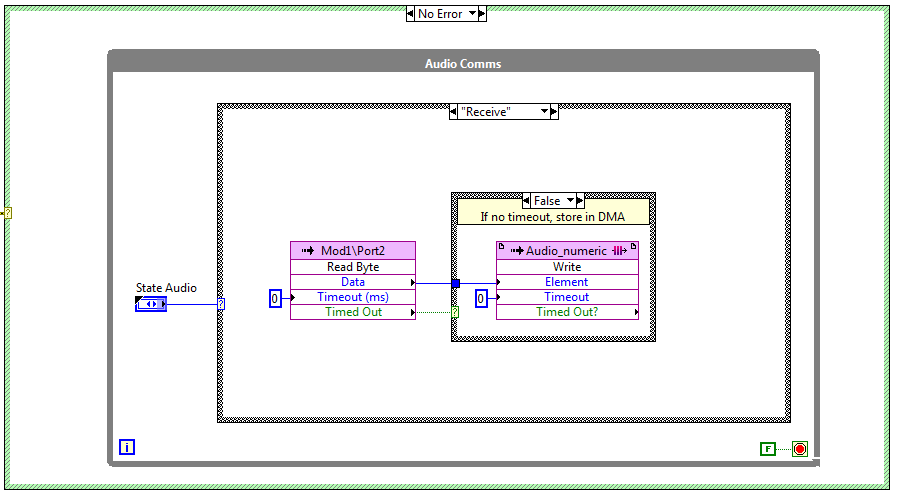

The problem is.... I loose lots of data. In fact, the first bytes (between 100 and200 bytes) are properly received, but then it starts missing bytes. The following picture shows how I designed the reading loop in the FPGA:

As you see the loop is very simple. It just reads the bytes and enqueues them in the DMA. The RT side reads the DMA, but as I said, the data read in the RT is not the data sent by the PC, data is lost (first bytes are ok, then information is lost).

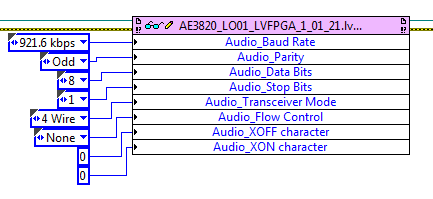

The port is configured in the RT side, as follows:

Messages are properly sent, since when I loopback my PC messages are properly received at 921600bps.

I am almost sure that the problem comes from the baudrate, since, when I modified the baudrate to 115200bps, the communication works as it should, the NI9871 module reads all the messages correctly.

However, I need to communicate at 921600bps. Theoretically, the NI9871 is able to work at that frequency. What am I missing? Does the NI9871 imperatively require to implement a flow_control mechanism to work at high frequencies?