- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI PXIe-7972R + NI 1483 cannot compile w/ Xilinx Vivado 2013.4

Solved!12-10-2018 08:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I'm using LabView 2014 and trying to connect NI PXIe-7972R + NI 1483 adapter to capture image from camera-link pco.edge camera. After install the driver of the PXIe-7972R, I try to compile the example target with "10-Tap 8 Bit Camera.lvproj" project. The PXIe-7965(with Virtex-5 FPGA) can compile off-line successful. However, when I try to compile the PXIe-7976R and PXIe-7972R FPGA target (both have Kintex 7 FPGA) with Vivado 2013.4, it doesn't work as attachment figure. I'm pretty sure the Vivado 2013.4 can support the PXIe-7976R and PXIe-7972R target (http://www.ni.com/product-documentation/53056/zht/), and I already install this compiler.

It seems Kintex-7 FPGA compiler have some problem, but I'm not sure.

The attachment are my error figure and code from example, thanks.

Solved! Go to Solution.

12-10-2018 08:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Almost looks like windows 10. I think that's only works with the newest compiler.

12-10-2018 08:54 PM - edited 12-10-2018 08:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, my OS is win10. But it doesn't work. I'm so frustrated.

12-11-2018 01:18 AM - edited 12-11-2018 01:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@volume2 wrote:

Yes, my OS is win10. But it doesn't work. I'm so frustrated.

Exactly! Windows 10 does not support your compile tools.

Follow the flowchart here to decide what to do.

(see also this thread)

12-11-2018 01:28 AM - edited 12-11-2018 01:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Seems cloud compilation is doable. Thank you very much.

04-10-2019 05:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

I have a simple FPGA program that compiles in cRIO without any problems, but I want to use the FPGA program on the NI 9144 EtherCAT Expansion Chassis in FPGA mode to NI PXIe 8135 (Code file attached). As you know there are some differences between programming the local FPGA and the FPGA for EtherCAT RIO, that must be used user-defined I/O variables (this paper).

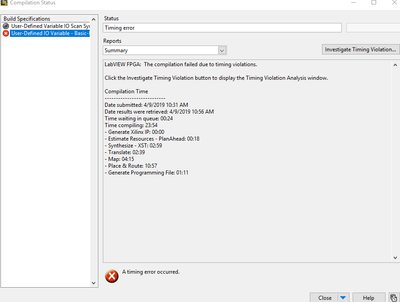

For Compiling I did step by step as this paper said, we get successful processes, but after file generation complete we have an error (that attached). It shows that the file can not run in chassis.

Please help me.

Regards.

04-10-2019 05:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This thread is already marked as solved. No one is going to come in to view and help. I suggest making a new post for your specific problem

04-10-2019 06:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I haven't use PXIe 8135 before. I think might be you can click "investigate timing violation" to see where is the error from. For FPGA/Host data transfer, I usually utilize FIFO for fast data transfer.

Best,

Yong

04-30-2019 05:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

I found the solution for Timing Violation Errors, In this link ( section 4)

The following are suggestions for improving timing in your FPGA code:

- Adjust the build settings to optimize for performance (Note: this may increase compilation times, and may result in area trade-offs).

- Optimize your code. Try the following best practices and optimization techniques within your LabVIEW FPGA code.

- Reduce the amount of logic in the VI

- Add pipelining to increase parallelism

- Use Timed Loops instead of other loops

- Change arbitration settings

I just use Timed Loops instead of other loops, so the compilation runs successfully.

Regards.

04-30-2019 08:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Congrats, thanks for your sharing.

Best,

Yong