- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 9234 : sampling rate : cRIO, FPGA

Solved!08-01-2013 12:12 PM - edited 08-01-2013 12:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

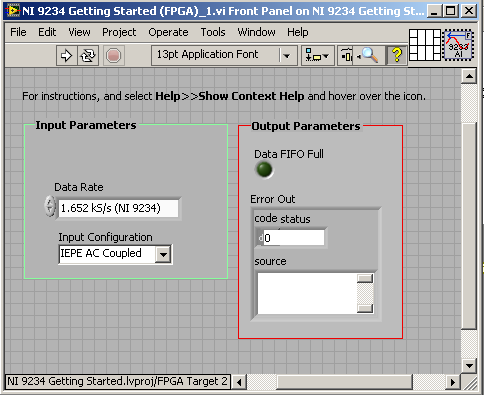

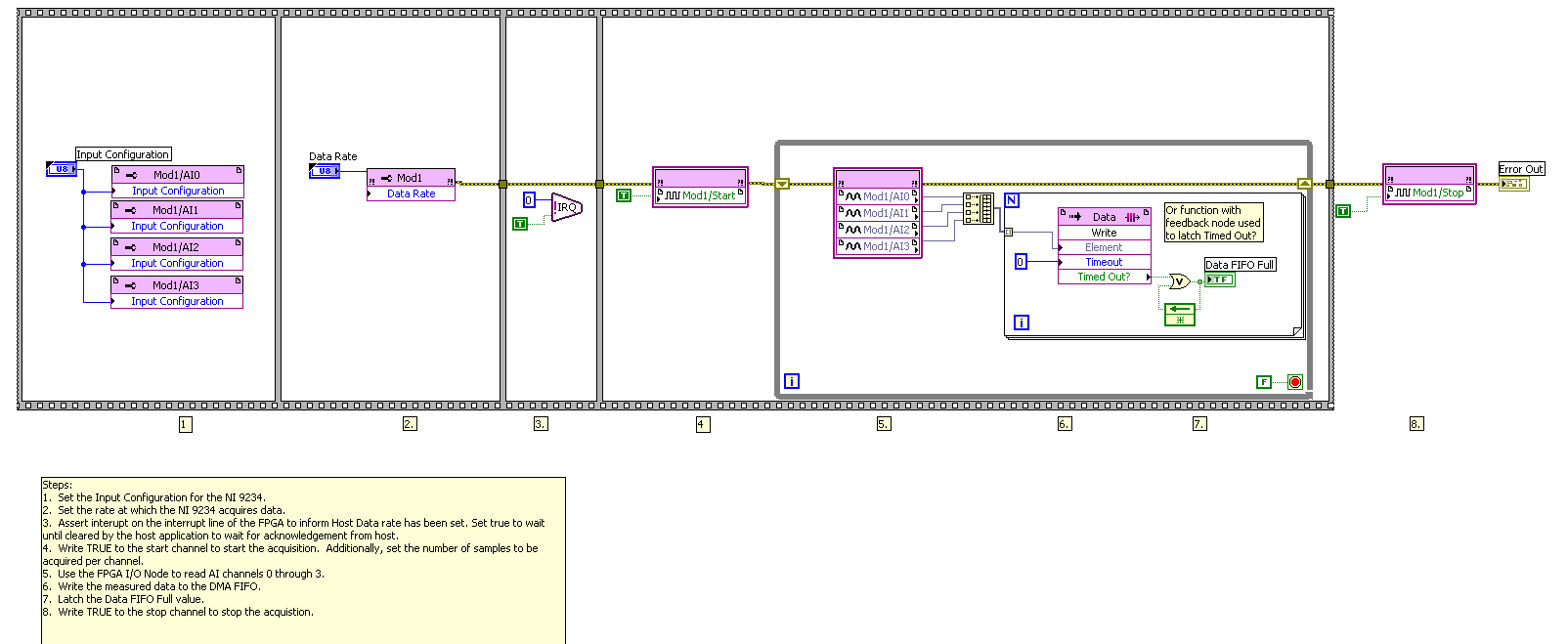

For NI 9234 module, front panel and block diagram of my FPGA code of my cRIO is like below.

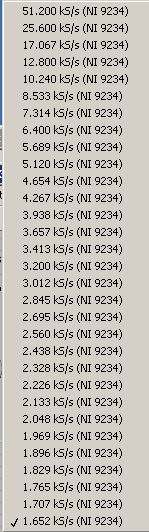

The sampling rate (data rate) is selectable between some values as shown below.

Do you have any idea how I can do the sampling with a lower rate that is smaller than the samllest option (1.652 KS/s)?

Solved! Go to Solution.

08-02-2013 11:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Cashany,

Take a look at this link. Page 16 describes the limitation that you are running into. Basically the master time base can only be divided down to certain data rates because of the way the device physically handles digital and analog filitering. So there really isn't a way to divide down past that point.

Applications Engineer

National Instruments

08-02-2013 11:14 AM - edited 08-02-2013 11:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks. I solved my problem by another method. My solution is in the following link:

http://forums.ni.com/t5/LabVIEW/DMA-FIFO-from-FPGA-to-RT-host-gets-full/td-p/2509316