- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Moving Project from daq to myrio

Solved!06-09-2018 06:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

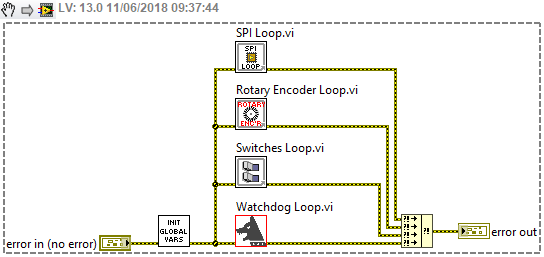

Hello everyone, I have a project to control a robot arm, I have already done a labview program to control it using daq 6221, the project has many VIs as shown in the screenshot.

Now i am changing the controll to myrio to work on fpga

My question is can i do that whole program on the Fpga ?.. I tried to do that but there was a problem that the fpga can't run more than one VI at once, I had to stop one to run the other

Hint: the robot needs to run all VIs Together parallel ,can't run one without the other

Solved! Go to Solution.

- Tags:

- fpga

06-09-2018 10:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

A myRIO project will happily run more than one VI. The key distinction is the 'top-level'. There can only be one top-level VI running at a time on an RT system or FPGA (one each), so you'll need to create a single VI that calls all of the others, and ensure that the others can be suitably called as SubVIs.

In terms of moving to FPGA, it's likely you'll need to reprogram at least some of the code. DAQmx isn't available on FPGA and only on a subset of RT systems, which don't include myRIO.

You can use either the Scan system, or program directly at the FPGA level, which is likely to be a bit different in terms of mindset.

06-09-2018 03:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So If i make a Top level Vi and compile it on the fpga and sub VIs on the FPGA Target "Without compiling" and put them in the top level vi .. that would work probably ?

06-09-2018 08:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you make one VI which calls multiple subVIs on FPGA, then when you create a Build Specification for the main (top-level) VI, the compilation will include all of the VIs (subVIs) that it calls.

This means that if you change the main VI, or any of the subVIs, the FPGA bitfile (basically the executable) will need to be recompiled. Be careful - this can be time consuming (for my project, which doesn't have that much code, a compilation takes ~8 minutes).

My second point before was that depending on your current code, it might be more or less difficult to move it to FPGA. Not all LabVIEW functions are available on FPGA (if you already know this and have fixed your code to work on FPGA, let me know and I'll stop saying so 😉 ) and so it will probably require modification to compile/run.

06-10-2018 12:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your reply, and yes i managed to convert the program into a fpga program.

also i made a top level VI, My problem is that i can't move the SubVis to the Top level Vi

No idea how to use them or move them on it.

Some SubVIs are not related to the top level VI, How Can I put them ( on a while loop or something ) ?

And if you have an example for what i am talking about Can you upload it please.

06-10-2018 07:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm not sure exactly what you already know and what you might have missed, so I'll just give some quick points. Hopefully one of them can help you get going again.

- To move a VI to the FPGA target, you can drag and drop in the project, using the item view (i.e. not the file view)

- It is possible to call non-FPGA VIs (for example, those on the Computer target) from the FPGA, but often these will break the FPGA VI due to unavailable functionality (for example, DBL data, variable length arrays, and so on)

- As you suggest, a bunch of While loops (either inside the subVIs, or around them) can make something continue running on FPGA. In lots of cases (perhaps or perhaps not your case) a False constant is wired to the Stop indicator, to make the loop run 'forever'.

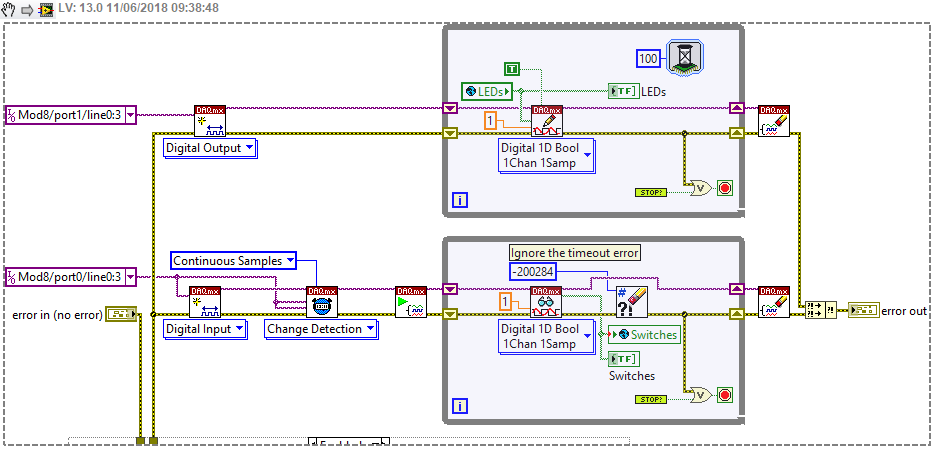

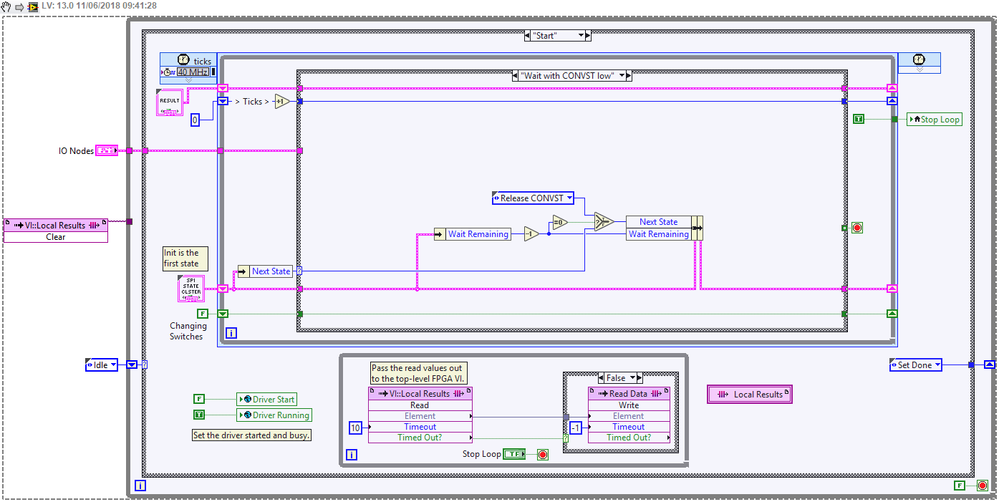

Here's a screenshot of some example code that I'm using. If you want to see an example you can interact with, I'd suggest taking a look at the template projects for cRIO or myRIO (I'm not sure which templates will be available for you - it depends on your LabVIEW installation, but there should be at least some).

Real-Time top-level:

Switches Loop.vi

and FPGA Main:

Part of the subVI shown (SPI Driver FPGA)

I know the RT examples show some DAQmx code after I went on and on about it typically not being available - I'm running this code on a cRIO-9045 which is one of the newer cRIOs with DAQmx available. Unfortunately, the myRIO doesn't have that capability (yet? I have no idea if that could change). I added the RT VIs because I think the architecture is similar to what you're looking for - a main VI which calls a bunch of unrelated VIs, which each run a loop. If you have any comments on my code, I'm happy for reviews/pointers 😉

06-11-2018 05:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you very much, your answers are very helpful and well explained, that helped me a lot doing my project. ![]()