- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Moving Average Filter

Solved!09-10-2013 10:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@sammir wrote:

THanks for all the reply. But this code is working fine in simple Labview but not in Labview FPGA. So please if some one designed the moving avarage filter in labview FPGA so please let me know. Or post the result or answer so that can be useful for otheruser also.

How is it not working? What error are you getting?

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

09-11-2013 08:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello\

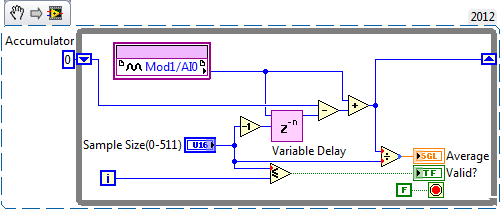

Please check the attached pic.

And in place of array I wanted to connect the analog input from the FPGA for example two channels. So please suggest the solution.

09-11-2013 08:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@sammir wrote:

Hello\

Please check the attached pic.

And in place of array I wanted to connect the analog input from the FPGA for example two channels. So please suggest the solution.

Do you need to have a variable sample window? For FPGA programming it is better to pick a sample size at design time to save space. The prior implementations I posted will work for static sample sizes.

You may be able to use the Xilinx RAM based shift register for a variable delay with the subtraction portion depending on what chasis you have.

09-11-2013 09:15 AM - edited 09-11-2013 09:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes I need to have variable sample window. So please can you attach your program VI so I can test it for my target. So I can see the result and what I am doing wrong

I have cRIO 9082 Chassis with 8 slots.

09-11-2013 09:34 AM - edited 09-11-2013 09:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@sammir wrote:

Yes I need to have variable sample window. So please can you attach your program VI so I can test it for my target. So I can see the result and what I am doing wrong

I have cRIO 9082 Chassis with 8 slots.

This should work, although it is untested. You can duplicate the Z-n blocks for more delay(sample size). If you use powers of 2 for sample size you can use a bit shift to do the division and save space. The average won't be valid for the first n samples.

Edit: Had the subtract inputs swapped.

09-11-2013 10:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I guess I ran out of edit time.

Actually the decrement on the input of the Z-n is unneeded, the function inludes the 1 sample latency.

I would replace the divide with a multiply by reciprocal. With the reciprocal as a control loaded by the host system.

09-12-2013 04:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

I am agree with WillD but the problem is we can not use the other data type and FPGA only gives us output in the FXP format and processing the FXP data are bit complicated. Also I have tried your solution but for me its not useful but thanks fort the solution. If you have some idea then you can try the proposed example and see the result and let us know the solution.

So with the fig you can more clear.

09-12-2013 06:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That variale delay node is an FPGA IP. It can't run in a host. On the host side, you are going to need to implement the array manipulation I performed in my proposed solution.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

09-12-2013 06:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

09-12-2013 07:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Do you want to do the calculation on the FPGA or the Host? FPGA has been mentioned numerous times, so I figured you needed it in the FPGA.

On the host there are many ways:

Pass your data as an array, size = sample size, use the Mean.vi

Pass your data into a loop and for each sample use the Mean-Pt-by-Pt.vi

Use the array method shown previously in this thread.