- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Labview FPGA, Crio 9039, maxium speed

Solved!06-24-2022 07:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

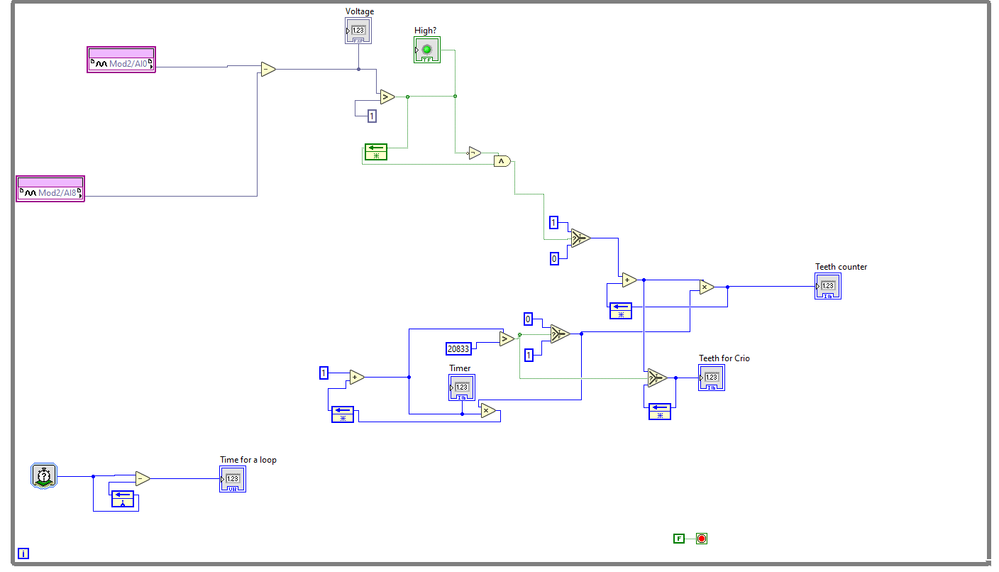

I'm using a Crio 9029 with a module 9205 ( 250ks/s). I put a square function supply on the 9205 to calculate the frequency. I did a very simple code. However when I reach the 9kHz, after it doesn't work anymore. I think it's problem of speef of the module?

Moreover when I count the time of the loop it is 48 us. But when I do it on simulation it's vers faster and I don't know if the compactRIO reaches his maximum but I don't think so.

So if somone knows why, it will be very helpfull 🙂

Best regards

Leo

Solved! Go to Solution.

06-24-2022 08:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Nothing here is screaming at me. But you could try going into the module settings from the project windows. You could set AI0 to be in differential mode, which would allow you to use just one read node instead of two. You should also make sure the Minimum Time Between Conversions is set to 8us.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

06-24-2022 08:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Thank you for your answer, for the moment I was in RSE mode. So I change in DIFF mode and I will try it. And yes, I put the minimum value time between conversion in8 us.

06-24-2022 08:37 AM - edited 06-24-2022 08:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I just did a little digging into the help and found this little bit about the 9205 sample pipeline:

To minimize the need for the pipeline updates, each FPGA I/O Node leaves the module pipeline primed to repeat itself. If you use only one FPGA I/O Node in a looping structure, only the first iteration of the loop will incur the two-cycle time delay. All subsequent iterations operate with no delay.

So you using multiple of the FPGA I/O Nodes does appear to be an issue here. If I am reading this correctly, it is taking 32us to do your readings when it should be in the 8-16us range. Setting the channel to be differential or expanding your FPGA I/O Node to have both channels would solve this issue.

EDIT: In case you want to look into it yourself, the article in the LabVIEW Help is titled "Conversion Timing for the NI 9205/9206 (FPGA Interface)".

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

06-24-2022 08:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

Okey thank you very much, I will try it now, but if the speed of reading it is 8 us, at waht is the 250ks/s in the datasheet? For me it is 250 kilo sample per second, so it can work with a frequency of 250 kHz.

If I want something with more speed I have to use a digital input?

06-24-2022 09:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

06-24-2022 09:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you very much. Now it's working, the time loop is 8 us now, before was 48 us.

Have all a nice a happy day 🙂

06-25-2022 11:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator