- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LV FPGA - Front Panel Strict Typedefs aren't flexible

Solved!04-08-2011 12:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

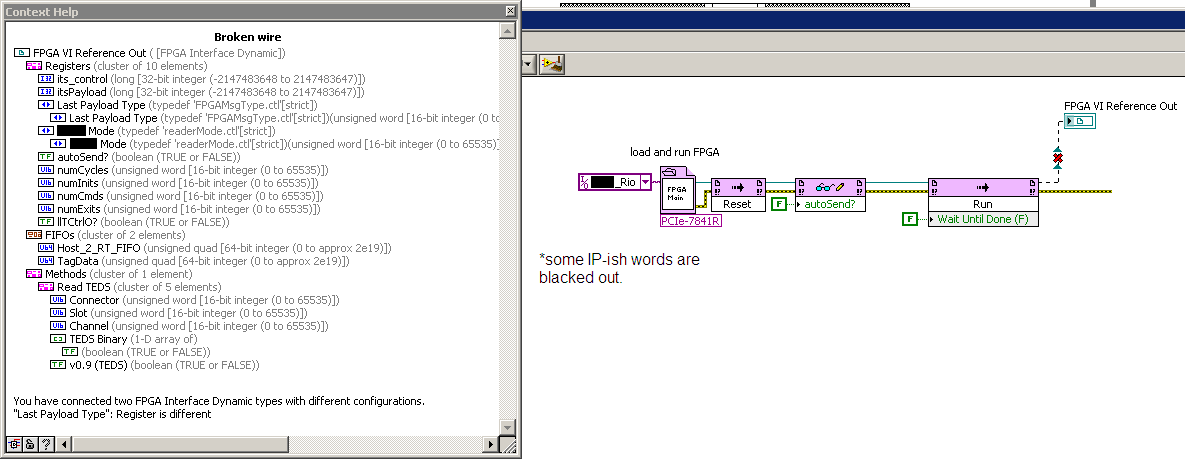

When using LabVIEW FPGA and implementing a strict typedef on the FPGA front panel, this causes issues with the FPGA Reference generated in the PC Code. I've attached a picture.

In my PC code, I generate the FPGA ref, then use it. In downstream subVIs I use the same ref. This works fine. But if I ever change the strict typedef and recompile the FPGA code, then I get the broken wire as in the attached picture. I have to manually recreate that FPGA Ref indicator, and cut and paste it into all the downstream subVIs, pain in the butt!

You would think that the strict typedef would not need updating in this manual fashion. Can you fix it in future versions, or am I doing something wrong?

Configuration Notes:

- Open FPGA VI Reference is from the bitfile, and in dynamic mode

- FPGA VI Reference Out Indicator is from the same bitfile

- Downstream fpgaRef indicators are from bitfile too.

Thanks,

Justin Reina

Solved! Go to Solution.

04-08-2011 02:58 PM - edited 04-08-2011 02:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Are you binding the FPGA reference to an interface, or to the VI? I would think if it's bound to the VI you shouldn't see this problem, but if you bind it to the interface this problem would be understandable. Also, have you considered making the FPGA Reference a type definition as well? Then you'd only need to fix it in a single location if it does break.

EDIT: in case it's not clear, by binding, I mean right-clicking on the indicator and choosing Configure FPGA Reference.

04-08-2011 03:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

alrighty now we're in business! For some reason I was afraid to make that reference a strict typedef. making it a strict typedef solved it!

still seems a little complicated, but oh well it works!

Thanks!

-Justin