- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Implement Filter and Dot Product in FPGA

08-30-2019 06:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Labviewers.

Actually I'm developing in sbRIO FPGA, and in my application I have to use a butterworth filter after a data acquisition and after that I have to implement a dot product.

The idea is to fill in an array, DMA with a certain number of filtered data.Once the array is filled i will proceed to make the dot product.

But I found that I cannot perform a butterworth filter and a dot product under the same loops, because, the filter node work in a while loop and the dot product only work under a while timed loop.

Should I do this in two differents VI that call each other when they finished or it is better do in the same VI? How can I do this, is there any module to call different VIs that works on FPGA?

09-05-2019 04:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@GuilleCad wrote:

Hello Labviewers.

Actually I'm developing in sbRIO FPGA, and in my application I have to use a butterworth filter after a data acquisition and after that I have to implement a dot product.

The idea is to fill in an array, DMA with a certain number of filtered data.Once the array is filled i will proceed to make the dot product.

But I found that I cannot perform a butterworth filter and a dot product under the same loops, because, the filter node work in a while loop and the dot product only work under a while timed loop.

Should I do this in two differents VI that call each other when they finished or it is better do in the same VI? How can I do this, is there any module to call different VIs that works on FPGA?

Review any examples related to your project. For example. there is a cross correlation example (uses FlexRIO) that is similar to dot product on FPGA, see that first.

Data on the FPGA should be streamed a few samples at a time. You should not fill up an array and then filter/process. This is 'software' thinking. On the FPGA, you have to think in terms of streaming data. Also allows for streaming and higher throughput.

You can use a Target Scoped FIFO to get data from one loop to the next.

On the FPGA you can have only one top-level VI running at a time so it has to be from one VI (they could be subVIs) but that may be too early for now.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

09-13-2019 07:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the reply.

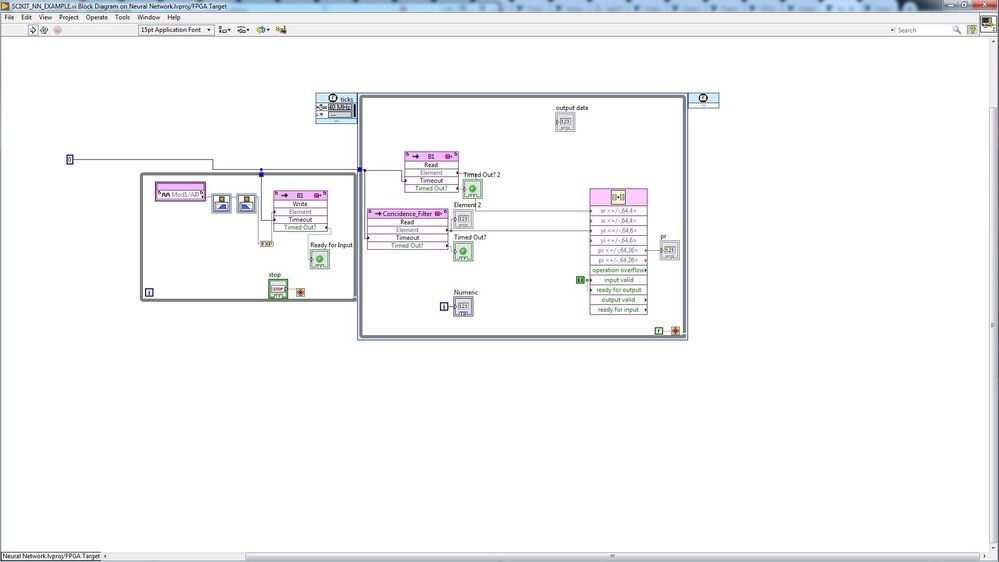

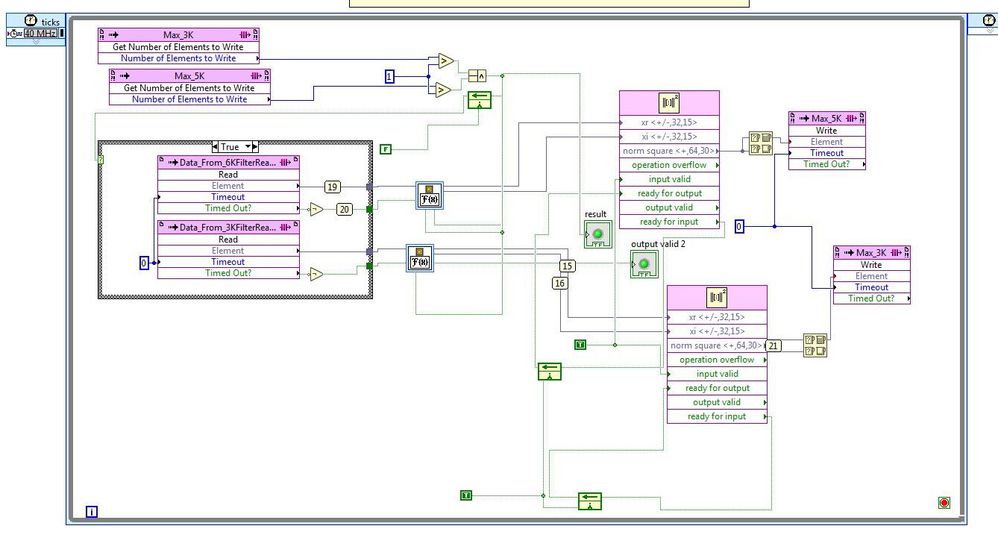

I implemented your solution of using an target scoped FIFO and put a Dot product into a time loop structure and it works.

es

Also i put the FFY module inside this loop and it works well, until it finish their calculation that it appears it does not reset the module to start a new calculation.

Any suggestion?