- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to solve error -61202 with using two FPGA references

Solved!02-28-2018 08:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

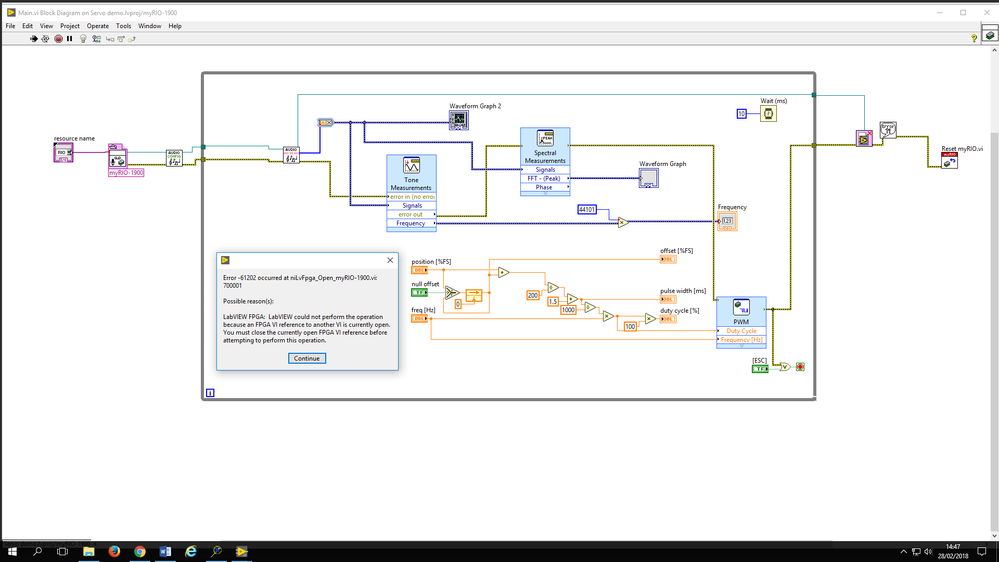

I met a problem when I programmed for myRIO in LabVIEW. I want to use myRIO to acquire audio data and produce PWM signals in the same time, to form a closed loop control for a robot arm with servo motor. But both the data acquisition and PWM signal production need to use FPGA reference, an error will happen, the error code is -61202. How can I achieve the function without making the error.

Solved! Go to Solution.

02-28-2018 09:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Did you try a reset? The program may have not stopped or closed out properly.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-28-2018 09:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you. I have added the reset outside the while loop, you can see my picture. It seems I cannot use 2 FPGA reference in the same time. But I don't know how to achieve the function without 2 FPGA reference.

02-28-2018 09:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I was not referring to the reset outside of the loop; just the old 'try a reboot' advice.

I only see one FPGA reference; not sure I follow. If you mean to fork the wire, then that can be done; just do not run Open more than once.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-28-2018 09:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There is a FPGA reference outside the while loop, and another FPGA reference is used in the PWM generator which cannot be seen. I have reboot the myRIO, but it doesn't work.

02-28-2018 11:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yeah, that's a problem 🙂 Reboot would not help that for sure.

Are there regular VIs that can give you access to the PWM? (i.e. non-Express VIs)

Also, an Express VI can be converted to a regular VI by right-clicking and selecting Open Front Panel, http://zone.ni.com/reference/en-XX/help/371361P-01/lvconcepts/create_expvi_subvis/

This is a one-way action but will give you access to the underlying LabVIEW code so you can modify it to not open the FPGA VI Ref twice but feed in the existing one.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-28-2018 02:53 PM - edited 02-28-2018 03:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have tried that, after I converted the VI to subVI, but it seems I am not allowed to modify anything in that panel.

03-01-2018 07:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Open the FPGA reference during initialisation of your code and then wire up the reference to both sub-VIs requiring it.

You can't deploy two bitfiles to a single FPGA chip. Deploy once and then re-use the reference.

03-01-2018 07:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you. I have solved the problem by using close FPGA reference VI to close one FPGA reference before opening another one in a while loop, but now my code only works when I turn on the highlight execution. It will not have error, but it will not show anything without highlight execution.

03-01-2018 08:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Quick question. Are the two bitfiles you are opening the same or different?