- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA to Integrated Circuit (IC) Possible?

04-05-2022 10:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, I know you can use LabVIEW to code for an FPGA but can you take that one step further and then make an IC from that code?

The idea is to prototype with the FPGA and then make it into an IC to mass produce. Has anyone done something like this and give some insights?

04-05-2022 02:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have never seen it happen but my guess would be that https://www.ni.com/en-us/shop/software/products/labview-fpga-ip-export-utility.html would be involved.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

04-05-2022 02:53 PM - edited 04-05-2022 03:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can of course do that but it won't be a straightforward process. But IC design never is. Basically with the IP export Toolkit you can create readable VHDL code from your VIs and then you can create netlists, convert them into whatever your software suite requires and import that into your IC design software suite of your choice. But if you really plan to go that route expect to spend a LOT more money than what you paid for LabVIEW, LabVIEW Realtime, LabVIEW FPGA, LabVIEW IP Export toolkit all together. Those IC design suites are not sold as standard software but usually leased from the actual IC manufacturer, on day, week or month base. And for more money than you would pay in lease for a high end sports car.:-) And you end up in the best case with ASICs. If you plan to do full custom design you would need to have a need for a few million chips per year to make that even feasible.

Basically it all depends on the number of chips you expect to produce. If its in the millions, custom design might be interesting', if it is several 10000 to 10000, ASICs might be doable, otherwise you end up with FPGA anyways. They are the standard for custom design hardware nowadays and only in exceptional cases would you go for one of the other solutions.

But the IP Export Toolkit is the first step to even think about reusing your IP in another environment than LabVIEW FPGA, even if you end up going with a Xilinx chip in the end yourself.

04-05-2022 06:45 PM - edited 04-05-2022 06:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

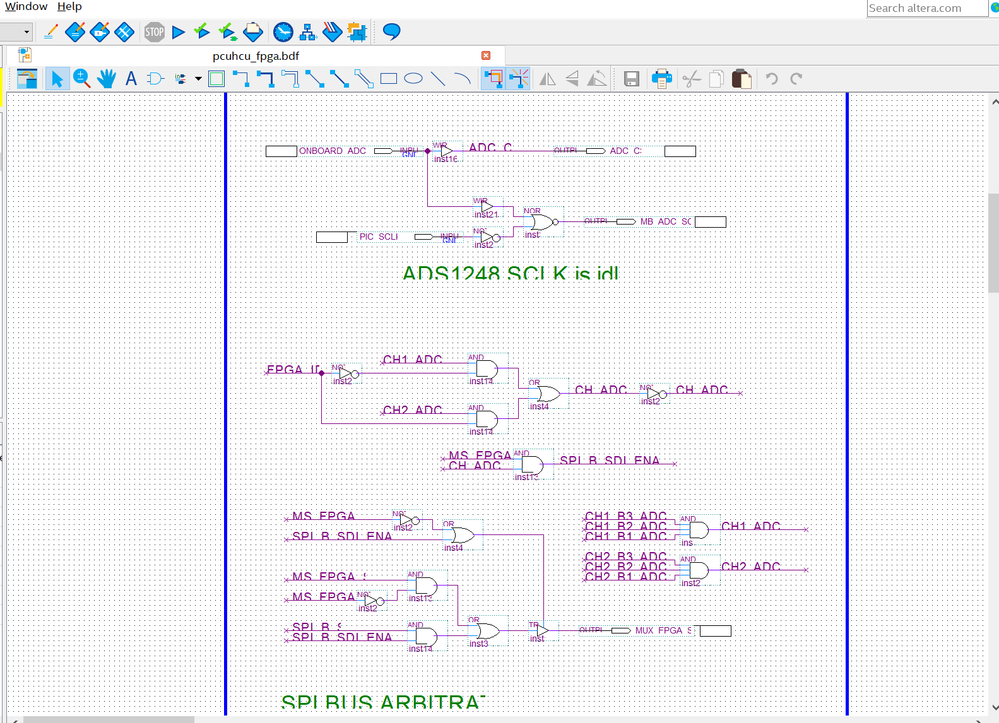

If you are going to to that you are much better off using a Hardware Description Language (HDL) in an environment like Quartus because you will be able to design the circuit using logic elements and IP that you will need to make the IC. Plus if you use Labview you have to buy labview real time units which are much more expensive than putting an off the shelf FPGA on a dev board, though finding an FPGA on a shelf these days is no easy task. Plus If you learn verilog you will have a job for the rest of your life, maybe not with labview.

Look it's just like labview, just wire it up : )

Have a pleasant day and be sure to learn Python for success and prosperity.

04-06-2022 05:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Mike,

Not my field of expertise but I think I have a basic understanding.

I believe no - my general understanding is that from VHDL you can prototype on FPGA and then use that to build an ASIC - I think this is what you are talking about.

With LabVIEW FPGA the generated VHDL is encrypted and not available to the end user - so you cant use it on targets other than NI FPGAs.

There is also nothing built into LabVIEW to let you target non NI targets (there are various abstractions for NI FPGAs that don't port to other systems).

========

CLA and cRIO Fanatic

My writings on LabVIEW Development are at devs.wiresmithtech.com

04-06-2022 08:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@James_McN wrote:

With LabVIEW FPGA the generated VHDL is encrypted and not available to the end user - so you cant use it on targets other than NI FPGAs.

That's where the LabVIEW FPGA IP Export Toolkit comes into play. It lets you basically export the encrypted VHDL code to readable VHDL code. However that code is heavily LabVIEW FPGA specific and won't usually be usable as is with other design environments. But that is anyhow often the problem with pre-existing VHDL. They seldom apply to your specific design without at least some cosmetic editing. VHDL for one isn't a very strict standard and each tool has its own dialect and specific datatypes and limitations.

04-06-2022 10:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

All we talk about is the logic that goes into the functionality of the device but miss out on the most important part of the chip design process - "layout"

This is the crucial part that uses certain "nm" technology to fabricate the p-mos and n-mos devices to make up the logic elements in your HDL or VHDL and the proper layout of these devices at the substrate is also important to achieve timing and parametric requirements.

Typically, you would choose the Fab for your device and get their technology details to start laying out the chip at the silicon level. I don't have any experience in this and I would not consider this something that can be "fully automated".

Soliton Technologies

New to the forum? Please read community guidelines and how to ask smart questions

Only two ways to appreciate someone who spent their free time to reply/answer your question - give them Kudos or mark their reply as the answer/solution.

Finding it hard to source NI hardware? Try NI Trading Post