- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA target to host DMA transfer speed

01-29-2020 07:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Guy, my hardware setup is:

1. NI5734

2. pie-7965r

3. pxie-1082

4. pie-8301

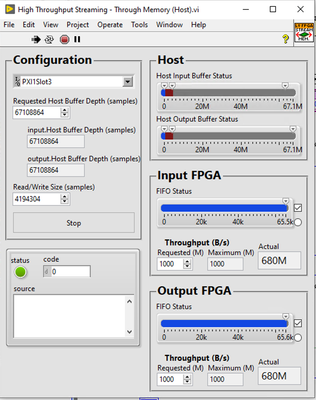

So, I used Labview example "High Throughput Streaming - Through Memory", it is stable at 680MB/s.

What I want to do is using NI5734 acquire signal with 4 channel, sampling rate 80MS/s(external clock), each sample is 16bit(2byte), which mean 4*80M*2 = 640MB/s. Is it possible the task be done by these setup?

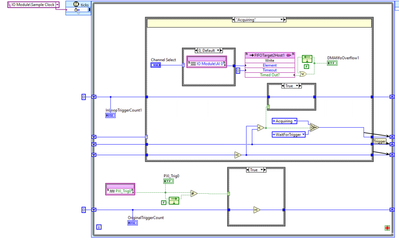

Let says that the trigger is 16kHz, each trigger(PXI_trig0) will collect 5000 samples, 16k*5k = 80MS/s. After I collect 5000 samples each time, I will use FIFO to send it to Host. To verify the task, I start collect one channel with 16kHz trigger first, 80M*2 = 160MB/s. Ideally it is far less than it max throughput 640MB/s, it should be work, but It overflow every time. It success unless I used 100Hz trigger for it.

02-05-2020 12:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Try increasing depth of FIFOs at host side it will let you store those 5000 samples until you read them.

But try reading FIFOs asap( I mean no delays in FIFO reading loop).