- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA - custom filter decreases sampling frequency by half

Solved!06-04-2019 03:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I've been designing an FPGA filter (compactRIO) for multiple channels, with BP IIR filter and RMS extraction over a period of time. It is enclosed in while loop and its iteration I believe is set strictly by reading from modules at its sampling frequency (102400 Hz for NI 9232). The problem is that when I introduce this filter, sampling frequency drops to 51200 Hz. As this cannot be tested in simulation, I tried simply disabling the filter with Disable structure and I had to compile FPGA for both scenarios. I cannot figure out what has gone wrong, could you take a look at the code? Is There is nothing I see that would cause the delay.

Thank you.

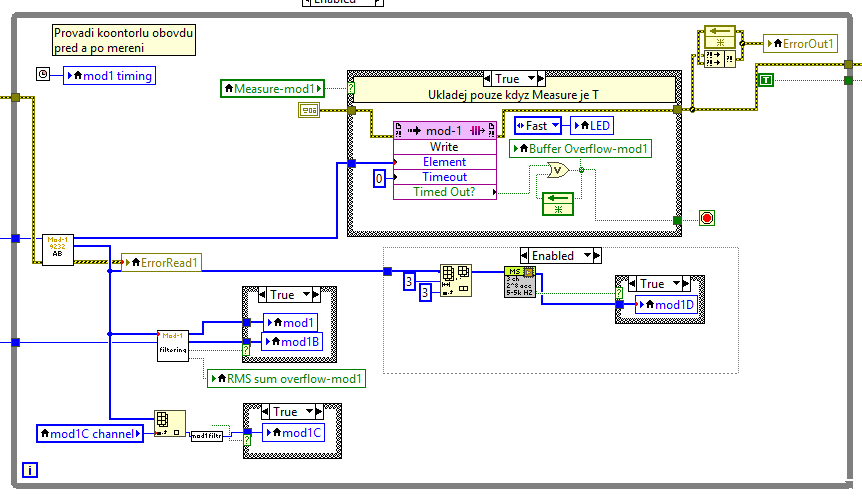

Main VI:

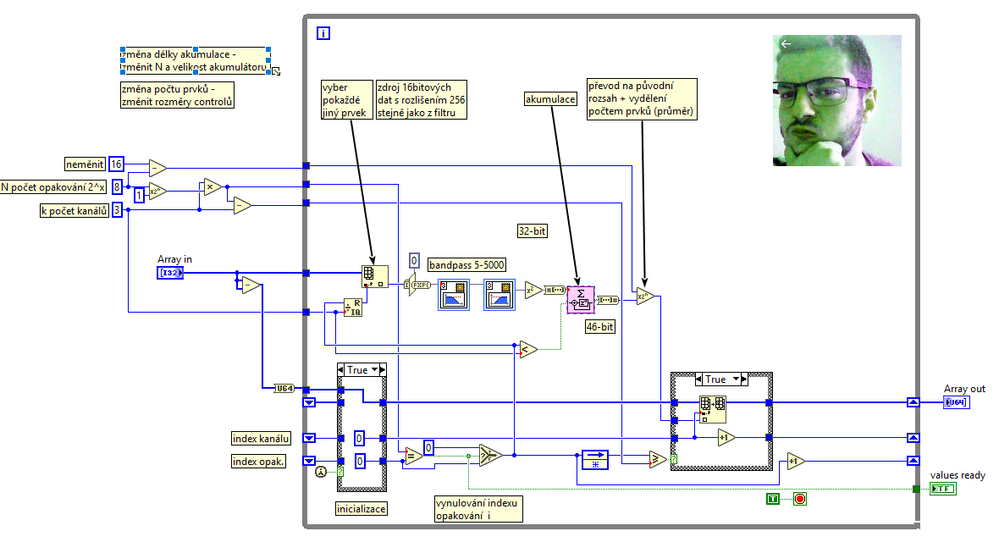

Filter itself:

(not me in the picture)

Solved! Go to Solution.

06-04-2019 04:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I only use timed loops.....

I think the amount of code in a normal while loop on FPGA will determine the maximum execution frequency available. This is because the code is essentially executesd sequentially. So adding code will slow down overall performance.

Or maybe not, like I said, I don't use non-timed loops in my FPGA applications. In a timed loop, timing is guaranteed (or it won't compile).

06-05-2019 04:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Most of the content I showed is just for illustrative purposes and I believe is not needed to be understood - just to make sure you won't find any major fails. The filter itself is FGV which is entered by an array of current data. Its elements run through two filters (set to multichannel), are squared and written to multichannel accumulator. The rest of it is only iterators and logic to achieve correct initialization and timing.

The main VI is simply reading data on the left and then writing to FIFO (top part) and also processing with three filters with front panel output (bottom part).

The important information i forgot to include is that the filter i am talking about is the grey-green VI in the Disable structure.

06-06-2019 03:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well if I don't need tounderstand the code posted, then the problem definitely lies within the "to Variant" conversion......

No seriously, assuming the code is in some way representative, I'm going to assume your actual code also runs in a normal while loop on the FPGA (as opposed to a single-cycle timed loop - SCTL):

Look HERE (from page 15-21) for more information on the differences between normal while loops and timed loops (tldr, timed loops are more difficult to master but offer FAR more performance). Due to data flow in a non-SCTL scenario, the number of individual nodes in your path will affect your end timing. This is because only one of those nodes is active at any given time. If your base clock is 40MHz and you have a series of 4 nodes after each other, your maximum execution rate will end up at 10MHz. If you have a series of 20 nodes, it will be only 2MHz. This is why I suggest you read up on this.

06-06-2019 09:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

My previous post was just a reply to AdamEvans explaning the code.

Thank you for the answer, this is obviously solvable by SCTL. I've heard about it and it is super not intuitive (just like all FPGA related) and as far as I know poorly documented, but getting into it deeper is probably the only solution.

06-06-2019 09:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Thomas444 wrote:

My previous post was just a reply to AdamEvans explaning the code.

Ah OK, that makes more sense..... ![]()

If you start down the SCTL route, good luck. It's not intuitive, but it's so worth it. ![]()