- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Timed Loop - Set dt

Solved!04-15-2014 08:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Whenever I try to use a Timed Loop in LabVIEW FPGA, it doesn't give me the normal options to set the "dt" instance. It works fine when I'm using timed loops on a Host VI, but not on the FPGA Target side.

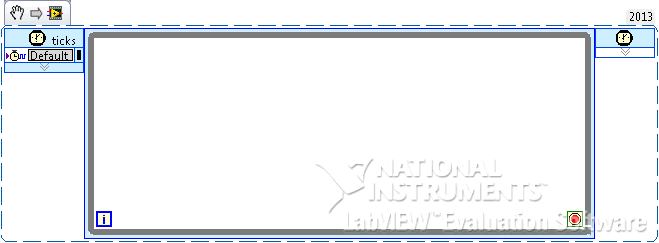

This is what I see:

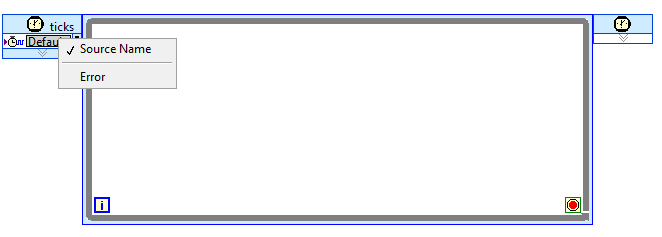

It shows the default clock as expected, but whenever I try to set another property, the only one available is the error:

Does anyone know how to set the "dt" timing parameter for a loop like this? Thanks in advance! 🙂

If someone helped you out, please select their post as the solution and/or give them Kudos!

Solved! Go to Solution.

04-15-2014 08:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

04-15-2014 08:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Where can the SCTL be found? This is the only timed structure I can find anywhere on the pallette. (If its not clear enough, I'm quite new to FPGA. I also am in the process of transitioning to 2013 from 2009 so its a bit different 😛 )

If someone helped you out, please select their post as the solution and/or give them Kudos!

04-15-2014 08:32 AM - edited 04-15-2014 08:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Asthma,

the SCTL (on FPGA) looks like the TWL (on PC/Realtime), we are talking about the very same structure.

BUT: on the FPGA that loop behaves different than you are used to from PC/RT!

Read the help!

Go through FPGA basics found here (basics, paragraph 6)…

04-15-2014 08:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That video was quite informative. Perhaps I have the wrong structure in mind then. My goal is to repeat a loop, say 10000 times at exactly 2 kHz. What would be the best approach to make this happen on the FPGA?

If someone helped you out, please select their post as the solution and/or give them Kudos!

04-15-2014 08:44 AM - edited 04-15-2014 08:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

04-15-2014 08:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Will do! Thank you for the help and sorry for the confusion. FPGA is quite a bit different than traditional LabVIEW on Windows.

If someone helped you out, please select their post as the solution and/or give them Kudos!