- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA ,RIO0 PCIe -7852R, Identifying data from DMA

11-01-2020 06:18 AM - edited 11-01-2020 06:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all;

I am working with LabVIEW FPGA, RIO0 PCIe -7852R, with digital signals.

and I want to transfer the data I received from the channels through DMA from the Target to the Host.

the problem is that I wanted to do this for multi-channels and my component has only three channels of DMA. So how can I transfer data from more than 3 channels using only 3 DMA's?

I mean, how can I transfer data from more than one channel to one DMA and know from which DMA the data came from when I extract it in the host.

Thank you.

- Tags:

- fpga

11-01-2020 11:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Aviran_Nunu wrote:

I mean, how can I transfer data from more than one channel to one DMA and know from which DMA the data came from when I extract it in the host.

There are some possibilities, but they depend a lot on your data types and sample rates

- Put your channels one after the other in the DMA, if they have the same data type and same sample rate (e.g. channel1, channel2, channel3 and always read (multiples of) 3 elements in the host)

- Combine the data types of your channels to a new data type if they have the same sample rate (e.g. two 8 bit integer and one 16 integer can be combined to one 32 bit channel)

- If the channels vary in data type and sample rate you can use an identifier (ID) for every channel. Use a big data type for the DMA and use 1 byte for the ID. In the host you can decide on the ID how to handle the remaining bytes.

11-02-2020 05:00 AM - edited 11-02-2020 05:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for the answer.

My data types are the same but the sample rates won't always be the same because my signals come in real time and not always at the same rate, most often it is at a constant rate but there can happen cases that the sample will not be at the same rate on all channels.

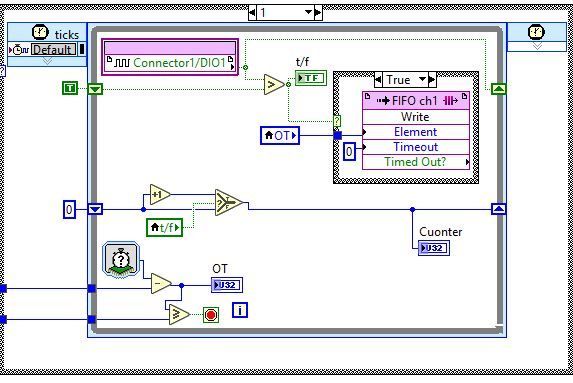

this is part of my code for one channel, I want to make it to more than one channel in one DMA

and know from which channel it came from.

PS, Can you please elaborate on identifier (ID)? Because I don't really know about it.

This is some kind of block or method?

I think it can help me.

Thank you.

11-02-2020 10:27 AM - edited 11-02-2020 10:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The ID could be something like in the picture I have attached.

Combine ID and your data in the FPGA and split it in the host.

One note to the local variable t/f in your picture:

You can not be sure if the read value is from the last iteration or the new value from after the greater comparison, because there is no data dependency (most likely it is the value from the last iteration, but I don't know). Use a direct wire either from the shift register or from after the greater node instead of a local variable.

11-03-2020 04:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you, I'll try it.