- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can I put all of my DAQmx read/write VIs in the same while loop?

Solved!07-26-2021 03:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am working on some code with multiple different read/write VIs. All channels will have the same sample rate, buffer size, etc., so I am wondering if I should lump them all in the same while loop.

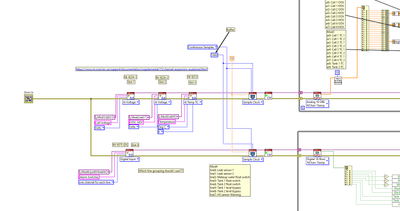

Currently my Read VIs are set up like this, and the Write VIs are set up similarly in another area of the code.

The main reason I would like to put everything in one while loop is because in the event of an error in the DAQmx VIs I want everything to shut down. For instance, the way it is now, if one of my Read VIs encounters an error but all the others are fine, then only that loop will exit, and I will need some sort of parallel communication to tell the other loops to exit. Putting them all in one loop would eliminate this potential concern because if there is an error in any of the DAQmx Read or Write VIs it can tell the whole loop to close. I think this will also increase the chances of my "Write safe states" subVI functioning properly as well.

My only concern with everything existing in the same loop is with timing. Like I mentioned before, all the Read and Write VIs will have the same sample clock settings, so I don't think this will be a problem, but I'm not certain.

Appreciate your help!!

Solved! Go to Solution.

07-26-2021 07:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm not immediately seeing an issue with it. I'd be more concerned with trying to actually synchronize your tasks. I'm not sure if you can with a cDAQ, but I would look into setting the sample clock for the digital input task to be the clock used by the analog input task. Then you start the digital task before the analog and then the samples should be taken at the same time by the hardware.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

07-27-2021 07:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@crossrulz wrote:

I'm not immediately seeing an issue with it. I'd be more concerned with trying to actually synchronize your tasks. I'm not sure if you can with a cDAQ, but I would look into setting the sample clock for the digital input task to be the clock used by the analog input task. Then you start the digital task before the analog and then the samples should be taken at the same time by the hardware.

Synchronization isn't absolutely crucial to the system, so if one reading is some amount of milliseconds behind another it won't drastically mess up my data.

Also I should have specified, I'm using a cRIO, not a cDAQ - not sure if that changes anything though.

As for your last comment about sample clocks, there's this article (https://knowledge.ni.com/KnowledgeArticleDetails?id=kA03q000000YHy1CAG&l=en-US) that shows how to sequence the DAQmx Start Task VIs for AI and DI. I think this accomplishes what you are talking about? My digital inputs are all safety features like level switches and leak sensors, so they aren't going to be phased. This leads me to believe that it's not that important that I time them perfectly.

07-27-2021 08:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@rseabeck wrote:My digital inputs are all safety features like level switches and leak sensors...

In that case, I would definitely keep them separate. Safety critical things should be either in the FPGA (my preference) or in their own loop in the RT. You don't want other things to possibly get in the way of them performing their task.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

07-27-2021 08:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Good point. I'll put them in their own loop separate from the other I/O devices. This will at least reduce the number of loops from one per channel down to just two.

Thank you!

07-27-2021 08:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Side note, yes the digital inputs are for safety features, but they're just warnings. Any critical safety features are run outside the program and shut off power to the system. I'm still going to put them in a separate loop I think, but just wanted to clarify that I'm not relying on LabVIEW to shutdown the system in the event of a critical safety issue.