- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Butterworth filters resources in Labview FPGA

03-28-2018 07:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I have a cRIO-9030 controller (FPGA Kintex 7-70T). I have 12 input signals in it, which I read at a 10kHz frequency. Every signal has a resolution of 24 bits for the word, 16 for the integer (24,16). I have some noise in the signals due to the nature of the system, so I need to filter them. To that end, I have included a 2nd order lowpass butterworth filter for each of the signals.

I can't implement a multi-channel filter because I do not want to loose signal resolution.

Filter coefficients (which may vary for each signal) are calculated in the RT side and passed to the FPGA via a DMA.

The problem is that even with just 12 filters (my first idea was to implement band-pass filters, so I would need 24), the resources (area) taken by the filters are too high, so the compiler is not able to fit the program in the Kintex 7-70T.

This is the compilation summary:

Final device utilization:

Slice Registers: 120495 (82000 disponible in the FPGA)

Slice LUTs: 75800 (41000 disponible in the FPGA)

I find 12 signals is not an enormous quantity of data and I am surprised to see that the cRIO9030 is not able to handle 12 filters, so I was wondering whether there is another way to implement the same thing without eating all the resources of the FPGA.

Any advice?

03-30-2018 03:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Anybody?

03-30-2018 05:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello I.Ayestaran,

Would you be able to send us your code (basic part of the filtering part that you implemented)?

You could do something like this to reduce ressource consumption.

Concerning the coefficient, I don't think you need to use DMA for this kind of data which are configuration and static and need to be defined only one time (RW Node instead of DMA)

Hope this will help.

Bye!

03-30-2018 08:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the response pierre.denis.

First of all, the link you provided me does not work for my case because I am dealing with 24 bit signals, and multiple-signal filters can only be used if signals are up to 16bit resolution.

Second, you may be right I could use another mechanism to pass the filter coeffs to the FPGA, but that would not fix my problem (I just check the DMA, if there is something inside I re-right my local registers in the FPGA, and if there is nothing in the DMA I do nothing).

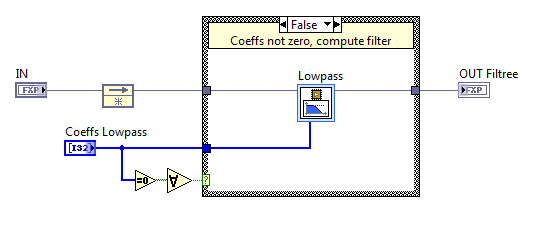

Here is my implementation for the filter:

I think the code it's pretty simple, I just call this VI for each signal (pre-allocated clone execution), at a frequency of 10kHz.

03-30-2018 10:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello afain I.Ayestaran,

Indeed, if you used Butterworth Filter IP in multichannel mode, you will need to use 16 bits FXP. Unfortunatly, this is a limitation you can't go around keeping the same VI. You will need to transform it in FXP 16 Bits.

I would advice you to use a different IP like the FIR Compiler. You will be able to fix both the depth and the number of channel (parallel or interleaved).

Hope it will fit your ressources.

Bye!

04-03-2018 01:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the advice PierreDenis, I appreciate your help.

I never used the FIR compiler. I just started configuring it but as it looks like I can't change the filter coefficients dynamically at run time. Am I right?

Iban