- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Broken wires with "Open FPGA Reference" connecting to a subVI

Solved!12-08-2011 04:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi All,

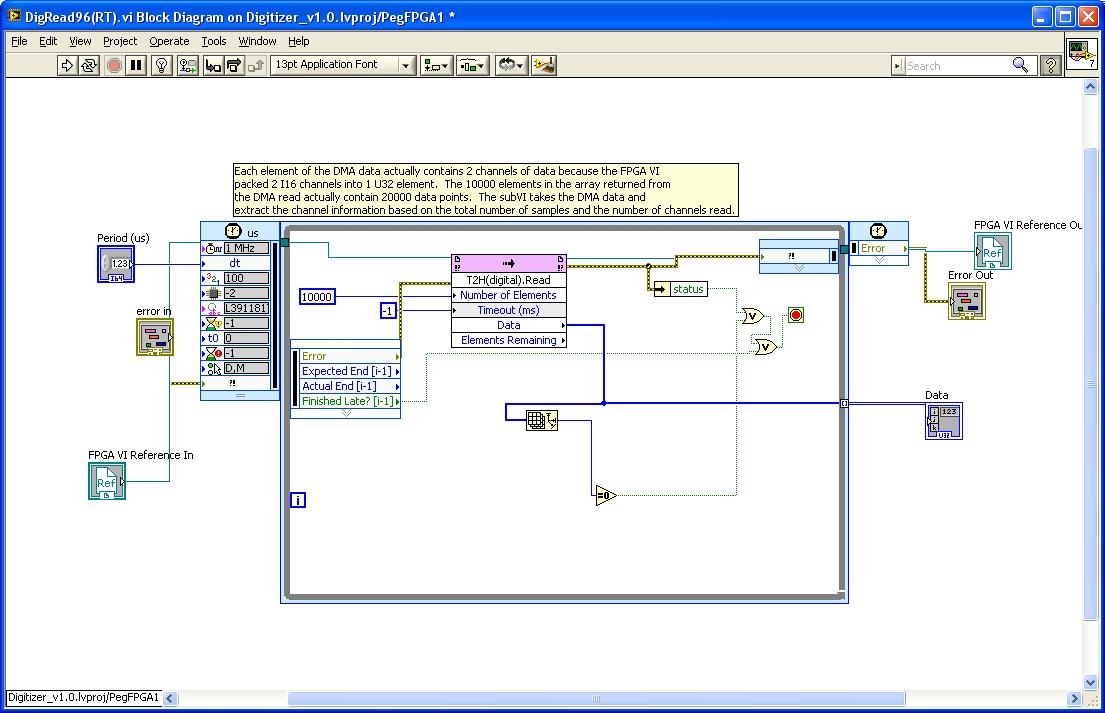

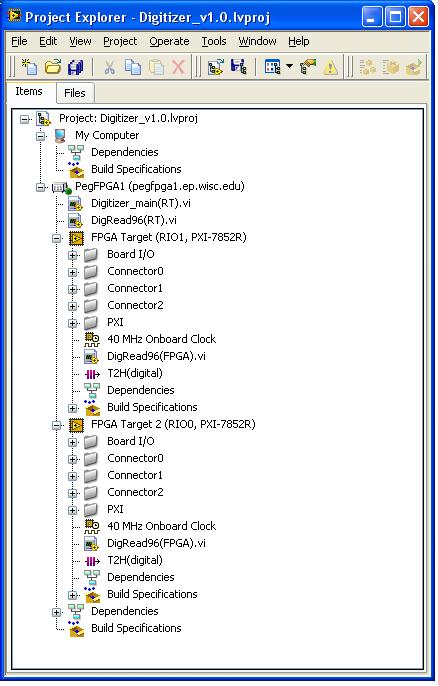

I'm using LabVIEW 2010, running on Realtime to recieve data from an FPGA. I'm attemping to pass an FPGA interface reference into a subVI that reads a DMA FIFO. Since I have 2 FPGA targets, I want to use one instance of the same subVI for each. I'm getting a broken wire between the "Open FPGA Interface" and the terminal of the subVI, although both data types are "FPGA Interface". I've googled this problem quite a bit, but none of the proposed solutions seem to work. I have tried using "Up Cast", to no effect. I also tried binding the FPGA host reference to a specific data type, but that didn't seem to change anything either.

Here are my VI and subVI. I appreciate any help anyone can give.

Solved! Go to Solution.

12-08-2011 05:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

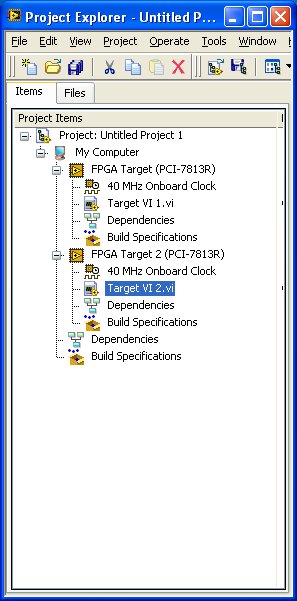

I have never tried to use two different targets, but since a FPGA Vi is essentially viewed as a piece of code executed on a target (thus compiled by the Xilinx tools and uploaded on the target), I would expect LV to need two different copies of the VI, each identified not only by the underlying code you have developed in LV, but most importantly, by the hardware address to the target. You would also need a separate FIFO to transfer the data from each device (according to your code, this is done transparently for you), etc.

So, bottom line, I would try to duplicate the VI and compile each one for its specific target (I would also have two targets in my project, as depicted below):

It is not a guaranteed suggestion, but did you try this approach? In particular, I would not exclude that you would need to compile the two VIs independently after having selected their individual target...

I'd be curious to hear about a more authoritative solution too!

12-09-2011 08:40 AM - edited 12-09-2011 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Try this.

Right-click the target and Configure Open FPGA Reference and make sure the Dynamic Mode is clicked.

www.southerndaqsolutions.com

12-09-2011 09:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Doug,

Thanks for the suggestion. Unfortunately I tried using Dynamic Mode, but it didn't fix the problem.

Justin

12-09-2011 09:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When you clicked dymanic mode did you replace you subvi FPGA reference control? The old FPGA reference control is not dynamic and will still have the broken wire until its replaced with a new dynamic.

www.southerndaqsolutions.com

12-09-2011 09:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

X,

Thanks for the reply. I do have two separate (but identical) VIs compiled on the two FPGAs. I am attempting to communicate with them simultaneously but separately. The subVI that won't accept the FPGA reference is on the RT host and the broken wires occur when I try to pass the two distinct FPGA references to the two instances of the subVI, whose purpose is to carry out the FIFO read.

JP

12-09-2011 09:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Doug,

thanks for the fast response. I'm not sure how to configure the FPGA refence control in the subvi, as it doesn't seem to give me any usable options when I click "configure FPGA VI refence" on the FPGA refence control in the subVI. Any suggestions?

12-09-2011 09:39 AM - edited 12-09-2011 09:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In the main VI, create a indicator from the open FPGA reference which is now dynanmic. Copy it and place it in the subVI changing it to a control and rewire.

www.southerndaqsolutions.com

12-09-2011 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Doug,

You were right. I found way to create a new FPGA refence control that was dynamic, and then it accepted the reference.

Thanks a ton!

JP

12-09-2011 09:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Glad it worked. I have been down this road before. ![]()

www.southerndaqsolutions.com