- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Best way to pass data from SCTL to While Loop

01-18-2022 05:49 PM - edited 01-18-2022 05:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

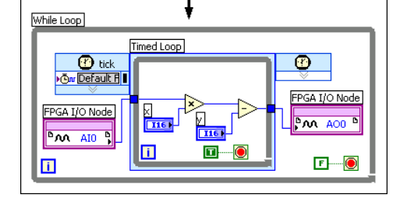

What's the best way to pass data from an SCTL to a While Loop? The While Loop is running slower due an AO node running at a sample rate of 1 us (1MS/s).

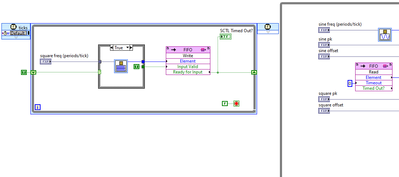

Currently, I'm writing data into a FIFO in the SCTL and reading out of the FIFO in the While Loop. I'm using handshaking to throttle data into the FIFO on the write side.

I'm using the 'Ready for Input' from the FIFO as a clock enable to disable the Square Wave Generator when the FIFO is full and not ready for data.

Is there a better way to pass data between different types of loops?

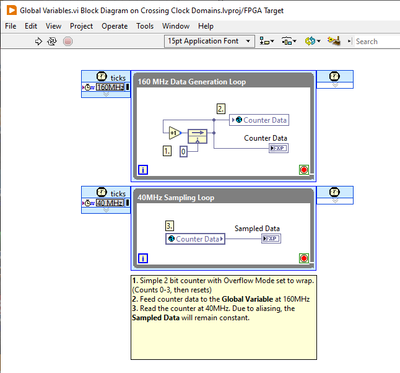

I noticed an example used a global variable to pass/cross data between clock domains. Is that a better approach?

If I used a global, does the Square Wave Generator still clock out data or does the global variable provide "back-pressure" and keep the Square Wave Generator from generating new values. I assume I want to provide some kind of clock enable to disable the Square Wave Generator when the Analog Output node/While Loop is stalled for 1us (40 ticks) between Samples.

- Tags:

- fpga

01-18-2022 06:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can read to or write from globals as fast as you want. You can write to it 100 times before reading if you'd like, so it will not throttle your write loop at all. The Read function always reads the most recently written value.

Why do you need to slow down the write? If the square wave generator is working appropriately at the correct actual frequency, it'll write to the global several times with the same value, then several times with the next value, and so on. Your AO loop will output the most recent sample. There's no need to ensure the AO will write each and every sample written in the main loop*.

One consideration is to make sure the square wave is generating integer samples. I don't know how fast your square wave is, but if it's close to the AO sample rate you will get aliasing.

*I don't have experience with the square wave generator you're using. If it just outputs a 1010101010 pattern then it won't work; I assume it's got smarts in it to output the right value at the right time.

01-18-2022 07:46 PM - edited 01-18-2022 07:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Based on what I've read, the Square Wave Generator uses Direct Digital Synthesis (DDS).

https://zone.ni.com/reference/en-XX/help/371599P-01/lvfpga/fpga_square_wave/

From what I understand, the Square Wave Generator runs continuously and every clock cycle the generator either generates –32767 or 32767 (I16). The issue is that the SCTL runs "out of sync" with the While Loop. While the Analog Out loop is stalled the SCTL continuously runs, cycling between values.

I had to move the Square Wave Generator to an SCTL because the generator stalls the While Loop for longer than 1us sample time and the samples to other analog outputs get output at incorrect periods. Seems like the Square Generator controls the loop execution rate.

When I placed the generator into an SCTL I noticed some jitter on the analog output. However, now that I read the documentation further, that might be expected.

Square Wave Generator Details section

"Over time, the Express VI returns the expected period length and frequency. However, some jitter might occur. For example, suppose you want to create a 6.25 MHz square wave using a 40 MHz top-level clock. In this case, a clock cycle is 25 ns and a square wave period is 160 ns, so the average square wave period should be 6.4 clock cycles long. Each square wave period is an integer number of cycles, but the Express VI returns period lengths of 6, 6, 6, 7, and 7. As a result, the average period length is 6.4 clock cycles, and the average frequency is 6.25 MHz."

Originally, I thought the small jitter I was seeing was due to the loop crossing. However, depending on the frequency setting, the jitter I am seeing may be expected after all.

01-18-2022 10:06 PM - edited 01-18-2022 10:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

According to this document

https://zone.ni.com/reference/en-XX/help/371599L-01/lvfpgaconcepts/using_sctl_optimize_fpga/

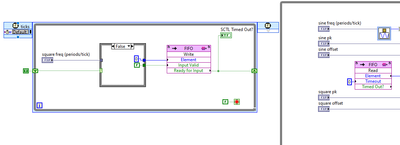

It looks like I can just set the Square Wave Generator to "single-cycle timed loop" and shove it in a SCTL with the conditional terminal tied to True. Then place the SCTL into the While Loop. The Square Wave Generator should only executes once inside the SCTL in one clock cycle. With this approach I can then get rid of the FIFO and handshaking.

01-19-2022 04:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@BertMcMahan wrote:

You can read to or write from globals as fast as you want. You can write to it 100 times before reading if you'd like, so it will not throttle your write loop at all. The Read function always reads the most recently written value.

Well, considering the lock-domain crossing, not every value written can be read so, depending on the throughput you need, itmight work or it might not work. Globals between clock domains are implemented behind the scenes as handshake items, with 4 wire control. This means that only every 3-4 cycles of the write clock will result in an actual chance in the recipient's data.

I found this out the hard way. If you're writing to the GBL 10 times for each sample, this won't be a problem, but if u're looking to get ever value written from every clock cycle, this wont work.

I have switched to using other methods. FIFO works, but also just BRAM, if you take care to not read and write from the same location at the same time.

01-19-2022 10:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ah, didn't know that. I hadn't considered the clock domain crossing effects of globals. Guess I"m still thinking in terms of desktop LV.