- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Acquiring synchronous signals from NI 9242 and NI 9203 IO modules

Solved!12-25-2017 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Our goal is to acquire voltage and current signals simultaneously. For this end, we are using NI 9242 for voltage measurements and NI 9203 for current measurements with cRIO 9063.

Separately, each module can perform correct readings (in terms of signal's amplitude and frequency).

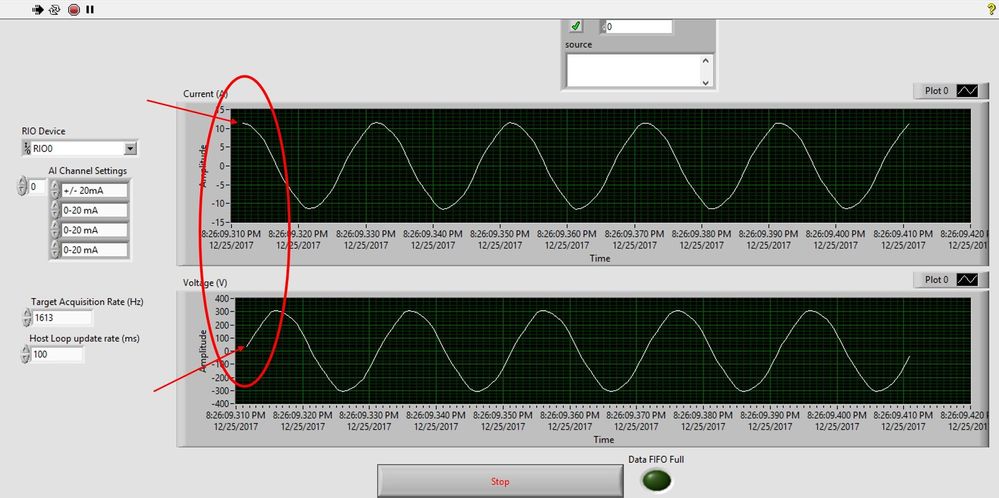

Though when used together in the same FPGA code, even if they seem to have correct sinusoidal shape, the acquired signals do not oscillate based on the expected frequency (50Hz), but 1.5Hz.

Another problem we are facing is the FIFO full error. Lately, it has been a constant problem.

We have tried to use different designs (number of FIFO used, number of IO nodes used, adding a wait function before starting acquisition in the FPGA code..). Nothing has worked.

P.S. In the host VI, we only specify the data rate of the second module (NI 9203, SAR ADC) and we ignore NI 9242's rate since it is delta sigma ADC (with minimum is 1.613kS/s). Maybe that's the reason why?

Please help!

The whole project is attached in this post.

Solved! Go to Solution.

12-25-2017 02:55 PM - edited 12-25-2017 03:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Updates:

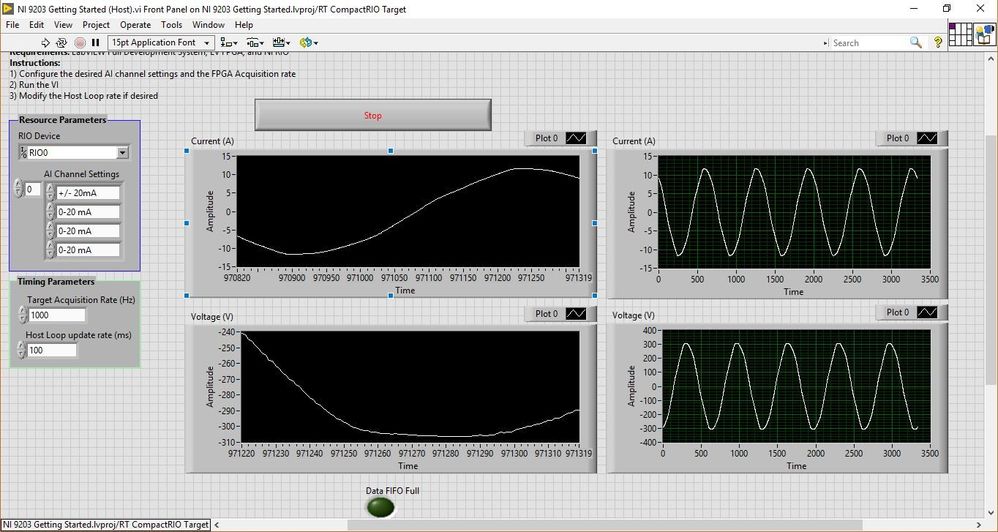

We were able to fix the FIFO Full and the fundamental frequency of the signals acquired (1.5Hz) problems by:

- Making a new project and adding only the VIs needed as opposed to the last project where we had many versions of VIs stacked in it. We used a FPGA code with 2 IO nodes and 2 FIFO, 1 for each module.

- Ensuring that both modules operate on the same Fs. This was done by specifying, with a constant, the Fs of the first module (9242) in the FPGA code, and the Fs of the second module (NI 9203) in the RT host VI. No FIFO error was encountered when Fs of NI 9203 is equal or less than Fs of the first module.

Now we still have the bigger issue which is having a phase shift between the voltage and current signal, as opposed to a in-phase signals since the load we are using is a pure resistive load.

Note that this phase shift is not constant.

Please help!

12-25-2017 08:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've answered this question before in another thread:

https://forums.ni.com/ni/board/crawl_message?board.id=250&message.id=91586

Section 4 in this white paper explains why you have the phase shift

http://www.ni.com/white-paper/11369/en/#toc4

Here's another option to fix the problem by adding a phase delay filter to the 9203:

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000P8cOSAS