View Ideas...

Active

Inactive

Inactive

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Unsupported nodes inside for loop within SCTL should result in a broken VI

Submitted by

EricLM

on

08-14-2019

10:15 AM

8 Comments (8 New)

EricLM

on

08-14-2019

10:15 AM

8 Comments (8 New)

Status:

New

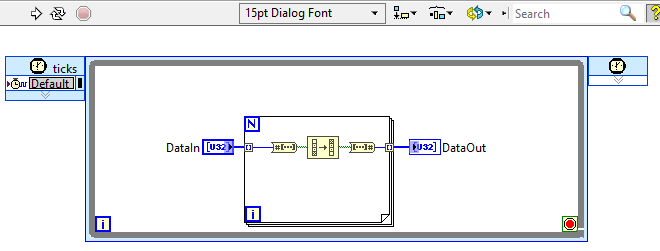

While for loops inside SCTLs offer limited functionality, placing an unsupported element inside the for loop does not result in broken code. Instead, one has to wait until the second stage of generating intermediate files to discover that the element is not supported. Code like the example below should show a broken run arrow if it is not supported.

Labels:

8 Comments

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.

Moving status to New since NXG has been discontinued and the problem still exists in LabVIEW.