- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

5641R External Clock

07-23-2012 09:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Recently we have met with an issue when using external sampling clock on 5641R. When we use 5641R Internal,everything is O.K. Signal we get is stable. But when we use External Clock (The “Clock In “ is connected to the Sine signal generated by Pxie5652,10dBm). Abnormal phenomena: The amplitude is not stable within the acquisition time. Settings: Ni 5640R configure Timebase.vi: CDC Clock Source=SMB External Ni 5640R ADC Configue NCO.vi: Previously Configured Clock Frequency= Sine signal generated by Pxie5652.

Would you please tell me how to solve it?

07-24-2012 08:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I would like to ask you a few questions and suggestions about your setup.

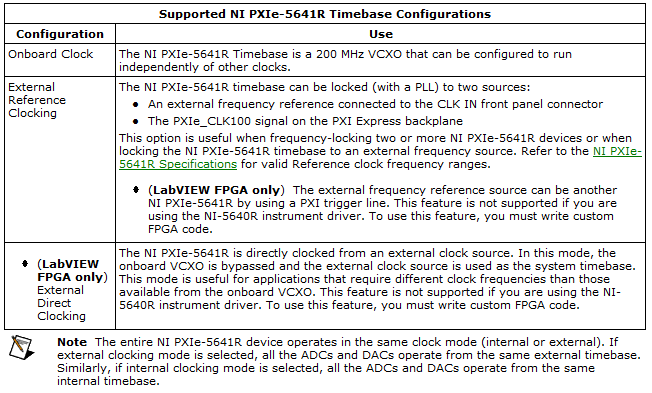

1) You have mentioned that you are using NI 5640R Configure Timebase.VI, Using this the clock that you bring in can only be used to PLL (Reference Clock). In order to use the CLK IN as an external sample clock, you will have to program in LabVIEW FPGA, based on the help documentation below:

2) If you are programming in LabVIEW FPGA, would you mind uploading your code, so I can take a look at it?

3) What is the clock frequency, you are importing?

Best Regards,

Jignesh P

Applications Engineer

Jignesh Patel

Principal RF Software Engineer

07-24-2012 04:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

After looking into this a little more, I realized that you are using LabVIEW FPGA to program. I would still like to know, what is the frequency for the CLK IN? Also, could you upload your code, so that I may take a look at it?

Best Regards,

Jignesh P

Applications Engineer

Jignesh Patel

Principal RF Software Engineer

06-29-2013 03:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator