From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

04-19-2014 06:04 AM

Hi all,

We have started working in NI-5640R IF-RIO with Labview-2011.

In our current setup, a 15 MHz sine wave is generated from a signal generator and it was connected with AI of 5640R.

Then we ran the buit-in examples and recorded the data in Measurement-File (ExpressVI) in TDMD format. The output tdms file was then analyzed using SCOUT software. (see Demo_setup.png).

After running various buit-in example we found that Driver>Stream-to-Disk example was running fine and input 15MHzCW sine wave was acquired perfectely by the 5640R card. (see Driver_Stream_to_Disk.png)

But there seems to be an issue/bug with FPGA>5640R & FPGA>5640R Async examples. THe problem is that when we anlaze the acquired sine-wane in SCOUT software there are jumps in the singal which means that after every DMA some inbetween samples are being skipped by the Device/HOST.

This is shown in the figures FPGA_5640R.png & FPGA_5640R_Async.png that after every DMA(5000) sine wave has jumps.

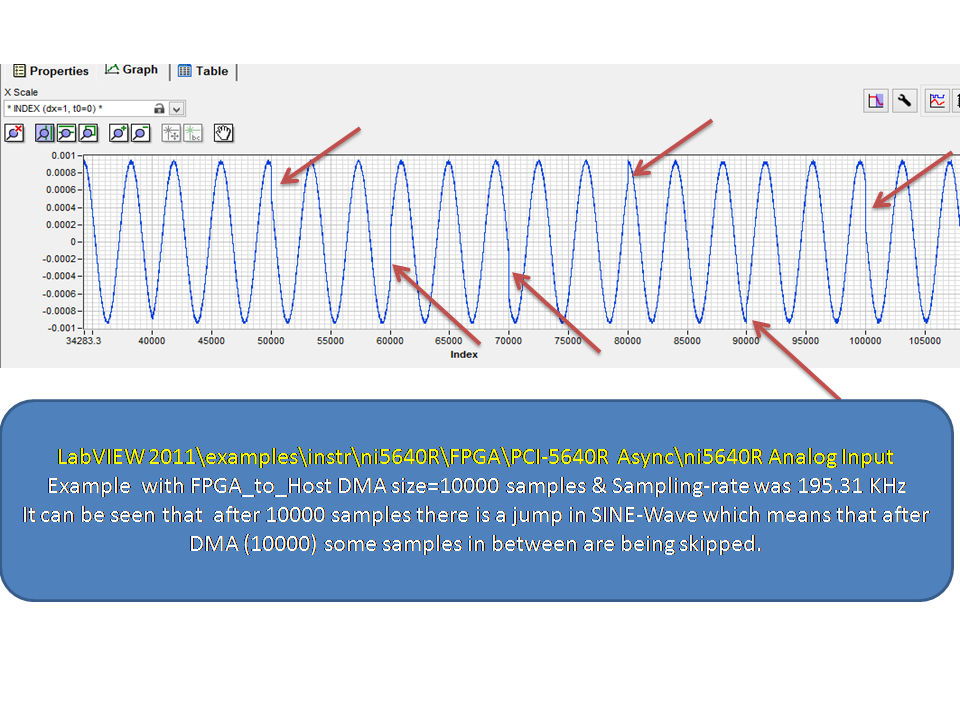

Afterwards we increased the DMA-size to 10000 and analyzed the captured signal again. It was observed that now the jumps in the sine-wave were visiable at 10000. (see FPGA_5640R_Async_DMA10000.png).

Can anybody explain this behaviour or what should we do to overcome this issue?

Thanks,

-Adeel

04-30-2014 11:35 AM

Hi Adeel,

Did you use the Asynch Analog Input Example as it is out of the box or did you make any modifications? When you are talking about changing the DMA FIFO size, are you referring to the host side or the FPGA? From looking at the example, it looks like the host buffer is set to 1M elements, and the FPGA side to 16,383. Is there a chance you are changing the samples to acquire (That starts at a default of 5,000)? Please send some screenshots to show me what and how you are modifying and I think I can help out better with that info.

Thanks,

05-10-2014 10:15 AM

Hi Chris,

>>Did you use the Asynch Analog Input Example as it is out of the box or did you make any modifications?

Yes i used it "as-it-is". Just added a Measurement-FIle at the I/Q output to visualize the results offline.

>>When you are talking about changing the DMA FIFO size, are you referring to the host side or the FPGA?

I am reffering to "DMA-Read Number-of-Elements" see image below. In examples this parameter is same as "AI-Samples-to-Acquire"

>>From looking at the example, it looks like the host buffer is set to 1M elements, and the FPGA side to 16,383

Yes this is correct and i didnot changed this settings

>> Is there a chance you are changing the samples to acquire (That starts at a default of 5,000)?

Yes by default it is 5000 and results were incorrect. Then i changed this to 10000 and 15000 and the results were same i.e. samples were skipped at multiples of this parameter (plz see my first post)

Using hit & trial, this issue was resolved if we disconnecnt "AI-Samples-to-Acquire" control from FPGA-parameter inptu setting, then the error disapered and now every-thing is working fine.

Thanks,

-Adeel