- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Phase lock to an external signal (6556)

07-22-2013 03:46 AM - edited 07-22-2013 04:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everybody,

I am using PXIe-6556 to simulate a slave transmitter device. To do this, I'am generarating a clock signal from a CMOS/TTL IC (VDD going from 1.8V to 3.6V) and need to generate a pattern from 6556 in a perfect synchronazation with the external clock edges.

This beeing said, I need to phase lock the onboard clock to the Master clock, or to use the master clock as clock source for 6556. Right?

So I've tried 3 solutions:

1) Since the Master used a PLL to generate the high frequency (50Mhz) clock, I used a 10Mhz clock (from an AWG) at its PLL input and I shared it with the CLK REF IN in the PXI Backpane.Then I selected the PXI CLK IN as reference clock for 6556.

Result: External IC clock and 6556 Generated pattern are synchronized, but in a random phase shift (data is not generated at a particuliar edge of the external clock).Whenever I re-run the VI, I can observe a different (but constant) phase shift. Is this the expected behavior of phase locking? If the phase shift is random, I can't correct it...I Need 0° phase shift, or if it is not possible, a constant shift through several VI runs.

2) I tried to use Master clock (50MHz) as clock in source for 6556. As a first step, using a AWG, I generated a 50Mhz square wave with a low state (0V) and a high state (3.3V). It worked fine. Next, I used the IC clock in the same operation (50Mhz at 6556 Clk in connector), but it didn't work. I had message talking about a clock that is not in spec... What's the matter? Maybe I need to set CLK IN at 1Kohm but how? I didn't find the appropriate VI to do switch to 1Kohm.

3) I tried to export the 10Mhz reference clock throughthe DDC connector (PF4) and to use it for IC PLL input. I thought I will certainly obtain a constant phase shift. Unfortunatelly, I observed the 100MHz clock comming out from PF4! This frequency is out of range of IC PLL spec... Is this a way to export the 10Mhz ref clock through PF4? (I need it from PF4 in order to control the High/Low voltage).

Thank you for your help.

Marwen.

07-22-2013 07:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Marwen

Let me try to address your questions. You are correct that the 6556 does have an onboard PLL. In your first setup you are overdriving the PXI Chassis' backplane clock with your 10MHz clock and then having the 6556 lock to it. The behavior you describe is expected. When you run the VI it requests the PLL lock to the reference clock which it is doing. While it is possible for the PLL to lock to your reference and generate a different phase output, the hardware is also performing other tasks which might account for your results. You should get less variability if you run your sample clock at 200MHz. Can you try setting your clock to 200MHz then repeating samples to get your 50MHz clock. You would need to use a data line to generate your clock pattern.

As a side note, you are able to move change the phase of the sample clock once it is locked. You can use the adjust sample clock relative delay function. However since the phase changes you would need to adjust before completing your test.

For your second question it sounds like you're trying to use the 50MHz signal from your master as the sample clock for the 6556. You were able to use an AWG at 50MHz but when switching to your device it stopped working. The clock in voltage limits are specified in the datasheet (i.e. 0dBm at 10MHz), but it sounds like you're meeting these requirements. It is not clear from your message if your clock is free running. Because of the internal circuitry of the 6556 your sample clock must be free running. If your sample clock stops you will get an error similar to what you described. If your clock is free-running I would expect this setup to work.

Finally for your third question you cannot export the reference clock to PFI4. The only place a reference clock can directly be exported in CLK OUT SMA. However if your sample clock is at least twice as fast as your reference clock you can use a data line and toggle it (1, 0, 1, 0) to generate the same frequency as your reference clock. If you ideally want to bring the reference clock in and generate a clock similar to the setup where you bring reference clock into the PXI Chassis Reference Input, but using CLK IN SMA I would try my advice from above were you set the sample clock rate to 200MHz to try and avoid the different phases.

07-23-2013 03:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jesse

Many thanks to your precious advices and clarifications. They will certainly serve me for my current and next projects.

Now here is my actual progress:

1) For the PXI Clk In reference senario: I found a way to measure (using a logic analyzer) the phase shift at each run. Now I can correct the phase automatically. I don't need to run at 200Mhz each time (by the way it is not suitable for me, because some times I need to generate some 43Mhz, 48Mhz...). Unfortunatelly, there is a huge jitter (2.5ns) when I observe the data generated from 6556 and the clock genereted by my IC (after being generated by its own PLL)... Where does this jitter comes from? I'm getting my 10Mhz from an AGILENT AWG...

2) The external sampling clock senario: I succeded to use the clock comming the IC. In fact, I set CLK IN impedance at 1Kohm and I inserted a serial 1Kohm at the other end of the SMA cable (next to the IC pin). I adjusted the delay, I now I have a perfect synchonized system.

But I'm still not satisfyed because I really wanted to work with the Reference Clock so I can control my own frequency.

Conclusion: I can realize my project using the senario 2, but it would be better If I can clean the jitter in the senario 1 and use the external reference clock.

Best Regards,

Marwen

07-23-2013 08:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Marwen,

In your setup do you reset your device, or does your clock go away? I just ran a test where I set my reference clock to PXI Clock and when I export sample clock and reference clock there is no phase shift between runs unless I reset the hardware.

07-23-2013 09:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jesse,

I'm not talking about a phase shift. I said that there is a jitter, a 2.5ns jitter. In other words, if I generate a 50Mhz sampling clock (locked to the reference clock) and in the other hand I generate from my IC (which has at its PLL input the same 10Mhz ref) that same 50MHz, and I observe the two signals, I can see that they are phase locked but with a jitter (vibrating slightly each one versus the other, I measured that vibration in terms on time, it was 2.5ns, which is too bad for my application).

07-23-2013 09:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Just to clarify, you are setting up one generation session and starting it once. You then look at the exported clock relative to your reference clock and you are seeing 2.5ns of varation in the phase difference between them? I would not expect this. Only if the device is reset or relocked would I expect the phase to change.

If you are getting 2.5ns of jitter between the two clocks, at least one of them must have a lot of jitter on it. Can you perform a jitter measurement on both the reference clock and the exported sample clock?

07-24-2013 03:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jesse,

Yes, I'm starting a contineous generation session. I've connected the ref on an AWG to the PXI ref. Then I generated 20Mhz (or even 10Mhz) from that AWG and put it at the input of the IC PLL. That PLL generates the IC 50 Mhz. From the other hand, 6556 uses PXI ref to generate a sampling clock at 50Mhz.

Comparing the two "50Mhz"s , I'm seeing a visible jitter of 2.5ns (not a phase shift).

The used IC a high performance circuit and we didn't see such a jitter comming from its PLL...

Marwen.

07-24-2013 07:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Marwen,

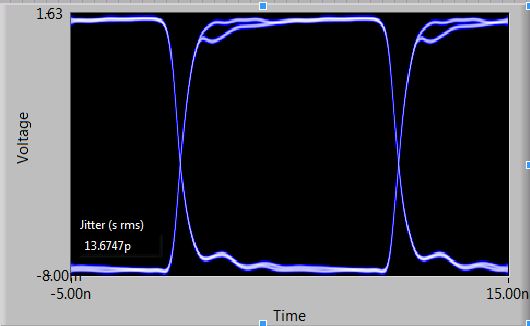

At the moment I do not have access to a chassis with a clock in function to drive the backplane, but I did take an AWG and generated a 10MHz reference and connected it to the PXIe-6556 clock in circuit (SMA connector). I then configured the 6556 to use the clock in as the reference clock. Next I generate at 50MHz signal and exported the sample clock. I connected the sample clock to a oscilloscope and generated an eye diagram and calculated the jitter. I've attached an image of the 50MHz clock output and there is not 2.5ns of jitter.

In your setup there is another piece to the clock path (the PXI chassis). Inside the chassis there is a PLL that takes your 10MHz clock and generates a 100MHz clock. The PXIe-6556 uses this 100MHz clock as the backplane reference. Can you connect your reference directly to the PXIe-6556 and try to reproduce my results?

07-30-2013 07:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jesse,

Sorry for this delay, I was a little bit busy studying the effectiveness of the chosen method (CKL IN as sampling clock).

Indeed, It is a perfect solution for our project and we already started working with it. So, for the moment I am in a develepoment phase and I am very loaded.

Concerning the "reference clock" solution, we decided to abort this alternative and to focus on the project progress with chosen solution. However, if I find a gap to reproduce your results, I'll do it and keep you in touch.

Many thanks again,

Marwen