Hi ademedeiros,

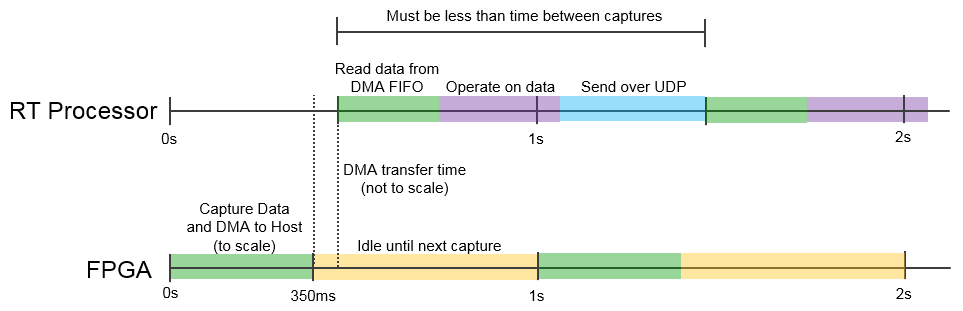

The FPGA to RT throughput will not be an issue to transfer 4.4 MB/s of data. Really, I think you would want to DMA the data immediately from the FPGA to RT for the 350 ms of capture time. That would mean a streaming rate of ~13.35 MB/s for the 4 channels. You would then have the time between captures to operate on that data and send it over Ethernet.

The SOM can certainly stream data from the FPGA to RT via a DMA FIFO fast enough -- that is not an issue. It is difficult to say with certainty that you can perform all of the math operations in RT in the given time span you require between samples. DSP operations can also be done on the FPGA before sending it to RT, which would significantly offload processing from the RT processor. Then, the processor would only need to read the data from the DMA FIFO and pipe it to the network.

In my diagram, I purposely did not put times on the FIFO read, DSP processing and UDP transmit as those are very dependent on your configurations. If you cannot close the timing between samples, you can either choose to lengthen the time between samples or move some of the DSP operations down to the FPGA.

Note: None of the RT times in the diagram are to scale, they just let me visualize what needs to happen before the next capture. Some of that may be able to be palatalized as well.

Tannerite

National Instruments