From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

01-28-2015 10:33 PM

Reply to this discussion with feedback for the NI System on Module.

03-17-2015 12:56 AM

Eric,

What exactly do you mean by Feedback?.

I love the SOM Concept it's something a few of my clients have been wanting for years. The package is awesome - well done!.

Would like to see a more powerful Zynq version come out, typically, we buy the highest performace sbRIO, cRIO for development to assure we have all the computing power avaliable. I've got two OEM projects where we are wincing already that it might not all fit or run fast enough on the current Zynq platform.

Direct access to DRAM via AXI buss on the FPGA might be nice. being able to access a large block of memory in the FPGA would provide a better path for one of our projects.

Regards

Jack Hamilton

03-20-2015 01:40 PM

Hi Jack,

I welcome any and all feedback, whether it is about futures, hopes for future variants, etc. I think the couple points of feedback you have given are great for this thread.

In regards to the more powerful Zynq version, are there any applications/tasks that you are struggling to meet with the current version or is it more about starting with the best and having a path to move down as much as needed?

In regards to DRAM access, can you share what pieces of the application (ex: vision processing) would benefit?

Thanks,

Eric

03-23-2015 07:16 PM

Eric,

We have an application that requires handling 32K point data matrix that requires parallel processing of 4-6 solutions. The ideal method would be to do DMA directly in the FPGA via the xlinix AXI bus to access the DRAM directly.

We've found the using the RT via DMA to 'manage the memory' of the FPGA is taxing on the RT and we need the RT to do other things.

As this project progresses, we are crossing our fingers that have enough room on the FPGA and RT to accomplish what we need.

The higher end xilinx Zynq has a substantial amount for more room so such tasks.

Regards

Jack Hamiltin

03-24-2015 01:47 PM

Hey Jack,

I'd like to understand a little better what you are envisioning. You are talking about it at a much lower level than the level of abstraction than we try to offer our customers.

"Direct access to DRAM via AXI buss on the FPGA might be nice. being able to access a large block of memory in the FPGA would provide a better path for one of our projects."

It sounds like you want the FPGA to access the DRAM so that you can transfer your matrix from the RT to the FPGA. LV FPGA has a DMA FIFO interface that sounds like what you are asking for. Is there something about that interface that makes it unusable for your specific application?

"We've found the using the RT via DMA to 'manage the memory' of the FPGA is taxing on the RT and we need the RT to do other things."

It's true that even if you use DMA FIFO's, it will still consume some processor time, and it's possible that your specific application is maxing out your processor or even the AXI bus. Do you have numbers on the throughput you need?

06-01-2015 12:24 PM

In sbRIO CLIP Generator, on the LabVIEW Interface page, I would like to be able to select the order of the pins that make up a UInt. Right now it defaults to placing the bits in the order of the DIO number. Buses are usually constrained by hardware layout/trace routing rather rather than DIO pin number.

06-01-2015 12:25 PM

Would like to see testbenching functional. Running the LabVIEW FPGA Desktop Execution Node with sbRIO-9651 results in error.

06-01-2015 01:50 PM

Thanks for the feedback and use case, LukeMSS.

-----------------------------------------------

In sbRIO CLIP Generator, on the LabVIEW Interface page, I would like to be able to select the order of the pins that make up a UInt. Right now it defaults to placing the bits in the order of the DIO number. Buses are usually constrained by hardware layout/trace routing rather rather than DIO pin number.

-----------------------------------------------

This functionality is available with the updates in the RIO 14.5 driver, so I would recommend updating to the new driver if you haven't already. This functionality is available in two ways.

1.) The order in which you select the pins for the integer is the order in which they will be added. For example, if you want an 8-bit integer to be pins 1,5,3,8,9,10,7,4 in that order, then you can click on those numbers respectively and the hit add.

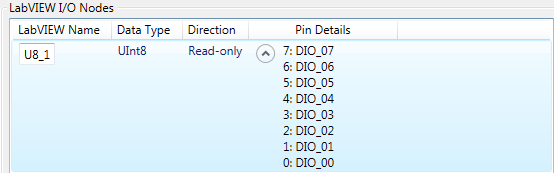

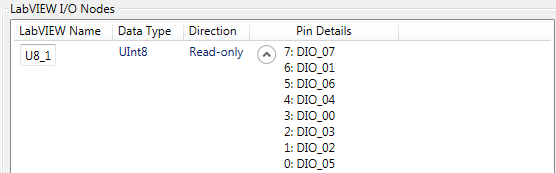

2.) You can modify the order of the pins in the CLIP Generator after adding them to an integer. If you hit the drop down arrow by the integer, it will show you a list of the pins. You can click and hold on any of the pins and drag them to a new location. Below is an example where I moved around the pins in an 8-bit integer.

Original

Modified

06-01-2015 02:12 PM

Luke,

The error you mentioned with the Desktop Execution Node has been recorded in Corrective Action Request 491843 and will be resolved for LabVIEW 2015.

Thanks

Bryan

06-01-2015 02:32 PM

That's fantastic. I thought I had the most recent drivers but apparently I don't. Thanks for the info, Eric.