- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can I disable clock I generated from/to CLIP?

12-06-2015 10:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear all:

I'm starting to use 9651 to generate clock from CLIP, now I have two question:

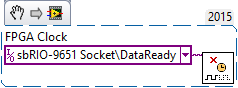

1, When I'm reciving clock from external source, can I use this function to stop my logical in the SCTL driven by external clock?

the DataReady is the name of a external clock.

2, I have generating clock from FPGA ( to CLIP), configured like below, it works, but I didn't find any option to disable the clock or configure the speed of that clock on the fly, do I missing something here? or it been designed to be like that?

Thanks!

12-10-2015 06:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi jiangliang,

1. When you are importing a clock through the CLIP into LabVIEW, you cannot use the Start Enabling FPGA Clock or Start Disabling FPGA Clock. This is stated in the LabVIEW Help for those VIs.

The functionality is not built into the sbRIO CLIP Generator to allow for a control line to enable or disable and imported clock.

The CLIP Generator using an IBUFG primitive, which you can see in the VHDL file generated from the CLIP Generator. An IBUF does not have an enable signal, it is just a global clock buffer to take the clock signal from the pin to the global clock network on the FPGA. An IBUFG is in the I/O Block near the pin you are importing the clock from. An IBUF is described further in the 7 Series FPGAs SelectIO Resources User Guide.

If you require an enable line, you could potentially modify the pre-generated VHDL in the CLIP to use something more well-suited to your exact functionality, such as a BUFGCE. The BUFGCE is not in the I/O Block nearest the pin you are using, but it is a dedicated clocking resource that is used to send a clock into the global clocking network of the FPGA (this is described in great detail in the 7 Series FPGAs Clocking Resources User Guide). The BUFGCE is a specific configuration of the BUFGCTRL Xilinx primitive, that has a similar behavior to the IBUFG that is pre-generated, only it has a CE (enable) signal.

You could modify the CLIP to instead use a BUFGCE with 'I', 'CE', and 'O' instead of the IBUFG. With that, you could use the sbRIO CLIP Generator to create a LabVIEW signal and modify the CLIP to route that signal to the 'CE'. The Xilinx documentation states that this should be glitchless by analyzing the timing diagrams, but the 'CE' signal will only affect the output on the falling edge of the input. I recommend looking through the linked documentation for more information.

A neat note here is that on the LabVIEW Interface page of the CLIP Generator, if you clock on the Data Type you wish, but do not click on any of the pins, it will create the VHDL and XML necessary for LabVIEW to see that node, and it will be available in the CLIP for you to modify. This could be useful for easilly creating a LabVIEW control signal to use with the BUFGCE.

I have not had a chance to try this, but this should give you some information to get started with. If you are not that familiar with VHDL, this may not be a viable option for you.

2. There is not an option in the sbRIO CLIP Generator to change the clock frequency of an exported clock on the fly. This uses an MMCM to generate a frequency off of the 40 MHz base clock, I believe. I was able to find some information about Dynamic Reconfiguration using and MMCM or PLL. You could potentially instantiate one of those into your CLIP, but would likely require intimate knowledge of both VHDL and the clocking resources available on the 7 Series fabric. I have not tried this, but here is the link.

Otherwise, you can create a derived clock that is much faster than 40 MHz in the LabVIEW Project and write some SCTL code to divide that down, but it will be in multiples of the 40 MHz base clock. The exported clock functionality is really meant to provide a fixed frequency clock to drive other peripherals.

-Tanner

National Instruments

12-12-2015 03:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you very much, you've been very helpful!