From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

By

Tariq Alshawi, Mohamed Elnamaky, Abdelouahab Bentrcia, Saleh Alshebeili

Prince Sultan Advance Technologies Research Institute (PSATRI), King Saud University

Riyadh, 11421, Saudi Arabia.

Products Used

National InstrumentsTM PXI-7842R RIO Card, Spartan 3E Starter kit, LabVIEWTM 2009.

Challenge

Select, design and implement a reconfigurable low complexity multiuser detector to overcome the problem of Multi Access Interference (MAI) in CDMA systems. The challenge facing any multiuser detector is to accommodate the maximum number of users but at the same time to be feasible for practical implementation.

Solution

Developing a solution that exhibits low computational complexity and high throughput to serve the real-time requirements of the CDMA system. That system is to be implemented on FPGA kits for the purpose of applying software defined radio (SDR) approach.

Abstract

Third generation mobile communication systems are CDMA based and therefore interference limited systems. In order to increase the user capacity and system throughput, interference reduction techniques have been developed and studied since 1986. An enhanced version of the SIC is selected to be implemented using a PXI-7842R. Results obtained from this work coincide well with simulations conducted using LabVIEW software.

Introduction

Code division multiple access (CDMA) systems currently employed in the third generation cellular networks is the framework of our project. Unlike the GSM networks where users are separated by time slots, the users in CDMA systems such as WCDMA are distinguished by different spreading codes for different users. Even though these codes are orthogonal, their orthogonality is destroyed by the severe multipath wireless channel and consequently MAI is created.

To overcome this problem, detectors taking into consideration MAI (known as multiuser detectors (MUDs)) are considered. Suboptimal MUDs such as decorrelator and LMMSE detectors exhibit moderate computational complexity and acceptable performance. However, their complexity can still be lowered by implementing them using linear interference cancellation (IC) detectors. After a long literature survey, the choice has been settled on a successive interference cancellation (SIC) detector developed and published by Bentrcia in IEEE communication letters on 2007. The IC detector selected for implementation in this work is a reconfigurable chip-level linear weighted SIC (CL-LWSIC) detector that can be set to converge to either a decorrelator or an LMMSE detector through a weighting factor.

This suggests its implementation using a software defined radio approach where detectors with different performance and complexity can be obtained by controlling the number of CL-LWSIC stages and by properly setting the value of the weighting factors. This project uses a National Instruments (NI) software/hardware platform available at King Saud University for the design and real-time implementation of the CL-LWSIC detector.

System Description

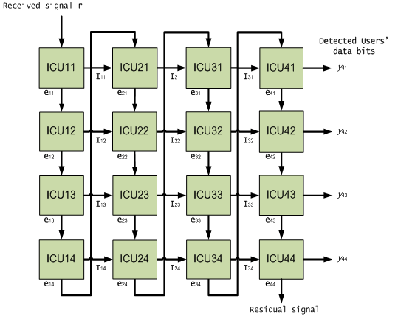

As depicted in Fig. 1, a multistage architecture using gold codes for the spreading/despreading processes consists of M stages and performs successive interference cancellation among K users is considered. In a SIC detection scheme, the interference Imk due to the user k at stage m is first estimated and then subtracted from the residual signal emk in order to provide the next user k+1 with a cleaner residual signal. This process is repeated in series for all K users and for M stages. At the final stage the user data bit of user k is obtained by taking a hard decision on the output ymk.

Figure 1: Multistage Architecture Of a 4-user, 4-Stage SIC Detector

Architecture Analysis

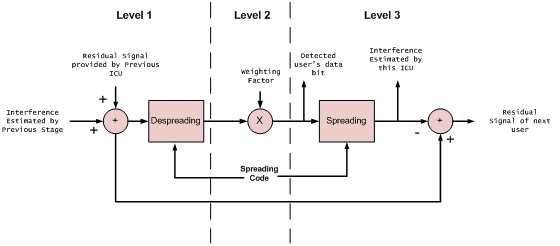

Targeting high throughput architecture, we applied both pipelining and parallel processing concepts. To analyze our design, let’s start with a single ICU. Fig. 2, shows that the ICU is divided into 3 levels of pipelining processing. This separation is based on a nearly equal processing time for each level. We replaced the multiplier inside the spreading/de-spreading blocks by simple multiplexers to serve that purpose. We added a counter inside the ICU to generate the control signals that synchronize data entry at each level. We did not use block RAM memories to avoid unnecessary delays that result from read/write processes. Instead, we used buffers with different sizes to synchronize data flow throughout the ICU.

Figure 2: The ICU Architecture Performs All Operation Within 3 Clock Cycles.

A single processing stage for K users formed by K serially connected ICUs, exploits the least latency and the highest throughput. To enhance the decoding process, we need to repeat processing the received signal over M stages. That repetition could be performed using a single stage in a feedback manner. However, high latency is generated as the number of users increase. Alternatively, we apply parallel processing concept using multiple processing stages to perform the decoding process. That increases the hardware resources consumption and hence; we tried to reach a balance-point among latency, throughput and hardware consumption serving the highest possible number of users.

Implementation Results

The design was fully modeled, implemented, and tested using only LabVIEW and LabVIEW FPGA. We extremely benefited out of the simplicity of LabVIEW FPGA blocks in the design of our CL-LWSIC detector. Architecture building was a straight-forward process and the FPGA implementation part took less than one month to be completed. This design was implemented and tested on Spartan 3E Starter kit which is fully supported by NI. For comparison, a second implementation was done on the PXI-7842R platform. Table 1 shows the results of a 4-user, 4-stage CL-LWSIC detector.

Resources | Utilization | Total number |

Total Slices | 52.5 percent | (15119 out of 28800) |

Flip Flops | 41.8 percent | (12041 out of 28800) |

Total LUTs | 49.1 percent | (14152 out of 28800) |

Block RAMs | 0.00 percent | (0 out of 48 ) |

Table 1: Implementation Results For A 4-User, 4-Stage CL-LWSIC Detector.

Critical path analysis shows that the minimum period for execution is 12.345 ns. Thus, maximum frequency is 81.004 MHz. Also, maximum path delay was 2.131 ns. The latency of the k user is equal to 2N – 1 (K x (M - 1) + k) clk cycles, where N is spreading gain, while throughput is fixed for all users at the rate of 2 (N – 1) fclk of about 1.35 Mbps in our case.

Conclusions

In this work, we designed and implemented a reconfigurable CL-LWSIC detector to combat the MAI problem in CDMA systems. The system was simulated using the LabVIEW and the architecture was implemented by FPGA module. Our next step is to implement the design on a Software-Defined Radio (SDR) System Based on the NI PXIe-5641R RIO IF Transceiver and test it in a real-time environment.

Acknowledgement: The authors acknowledge the support of KSU. The work reported in this paper is supported by KACST under project Number ARP 29-55.