From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

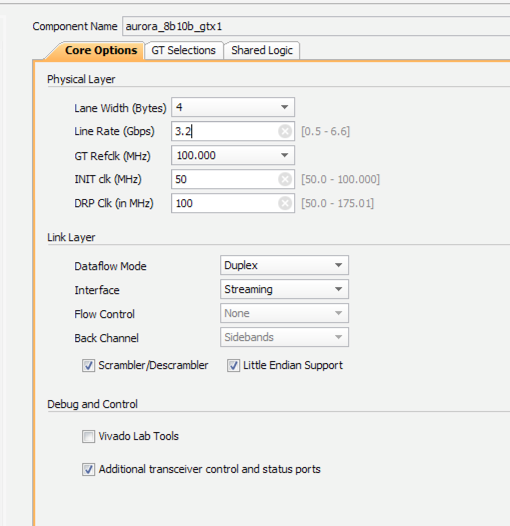

This project instantiates four individual Aurora 8b10b x1 cores on a PXIe-6592R @ 3.2Gbps. The LVFPGA diagram can generate and check patterns. This is intended as a starting point for customers needing to communicate to another Aurora 8b10b device. Each Aurora core is connected to an SFP+ port on the PXIe-6592R, and is capable of transmitting and receiving simultaneously. Please read the readme.docx included in the LabVIEW project before modifying the Aurora configurations in Vivado. The Xilinx .xci file is included in the zip file for the user to see the core settings or modify them:

Latest Version

PXIe_6592_Aurora4x1_ext_v1.zip

Software Requirements

LabVIEW 2015

LabVIEW FPGA 2015

Instrument Design Libraries for High Speed Serial Instruments 15.5

LabVIEW 2015 FPGA Module Xilinx Tools Vivado 2014.4

Hardware Requirements

NI PXIe Controller

NI PXIe Chassis

PXIe-6592R

SFP+ Cable

The attached Code is provided As Is. It has not been tested or validated as a product, for use in a deployed application or system, or for use in hazardous environments. You assume all risks for use of the Code and use of the Code is subject to the Sample Code License Terms which can be found at:http://ni.com/samplecodelicense

hi,

I'm the field sales in China, it really helps a lot. There are still two questions, can anyone help me ?

1.Whether the project is compatible with Xilinx' s LogiCORE IP Aurora 8b/10b v5.2?

2.If customer want to use the project with 2.5Gb/s, how to fix the code?

I know I can change the clock rate to change the transmission speed, but I would like to change the data width to change the transmission speed. For example, can 2.5Gb/s be achieved by changing the boolean array with element of 25?

Thanks for your help.

Hi Freedomxn,

Can you please email Chris Nunn with you questions? He is traveling and having trouble logging in. Thanks!

Hi,

We are now doing the evaluation of the NI 6592R card and I found this example really helpful. I am able to modify the core to make the card to run at 3.125 Gbps and 6.25 Gbps correctly. However, when I try to run it at 5 Gbps, it seems that the actual data rate is only 2.5 Gbps. The setting I am using for the aurora 8b10b core is as following:

Vivado Version: 2013.4

Lane Rate: 5Gbps

GT Ref Clock: 125Mhz and 250 Mhz respectively( try twice already)

GT Ref Clock From LabVIEW side: MGT Ref Clk 1 connecting to all four ports aurora instance

Can give any advice for solving the problem? Really appreciate any advice for starting the trouble shooting.... I have been stuck here for a while......

Best Regards,

Zhou Daquan

Hi,

Thank you for the proof of concept. We are interresting with AURORA communication through PXIe-6592R and XILINX IP but only in spy mode.

Do you think this IP will work as SPY mode on AURORA link (no emission to the other side) ?

Thank you for your help,

Best regards

Guillaume

Hi Guillaume,

As far as I can tell "SPY Mode" is not an official mode of the Aurora 8b/10b spec so can you explain a little more about your application (feel free to DM me)? In regards to one-way communication the spec does have an alternative Simplex Mode (see https://www.xilinx.com/support/documentation/ip_documentation/aurora_8b10b_protocol_spec_sp002.pdf#p...) however I believe this core still has some handshaking involved to determine a good link (though this may still work for your application so please investigate). If however your looking to analyze raw data streams, you can expose the MGTs used directly; see our MGT Debug example (https://forums.ni.com/t5/Examples-and-IP-for-Software/NI-MGT-Debug-for-the-NI-PXIe-6591R-92R/ta-p/35...) for more detail here.

Regards,

John G.

NI FlexRIO & High-Speed Serial PSE

Hi,

I need to reconfigure the IP core to 2Gbps of lane rate so I followed the instruction for using the Xilinx .xci file in the Vivado. I was able to regenerate the IP files inside the Xilinx folder, but after that, I realized the set of files used to import the SCLIP in LabVIEW is not the one inside the Xilinx folder, but the one in the CLIP folder.

The generated files:

The SCLIP files:

So it's not clear what should the next step to load my modification to the LV project. Maybe there's an additional step I'm not aware of.