Export a Clock Signal on FPGA Device

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW

Software

- NI RIO

Driver

Code and Documents

Attachment

Description

Description-Separate-1

Introduction

The following example outlines three individual methods for exporting a clock from an FPGA device. This example project was prepared using a PCI-7831R; however, may be employed on any FPGA reconfigurable hardware. The methods allow users to create a clock signal on a FPGA digital output line. The examples demonstrate the use of FPGA derived clocks, Signal Generation Express VIs, and PWM generation techniques.

Steps to Complete

1. FPGA Derived Clock Exported via Logic Not

a. Create a Single-Cycle Timed Loop (SCTL)

b. Place a Boolean constant outside the loop, to initialize the clock edge.

c. Place a 'Not' function inside the SCTL.

d. Use a shift register to continually update the boolean output.

e. Use a FPGA I/O node to write the digital channel.

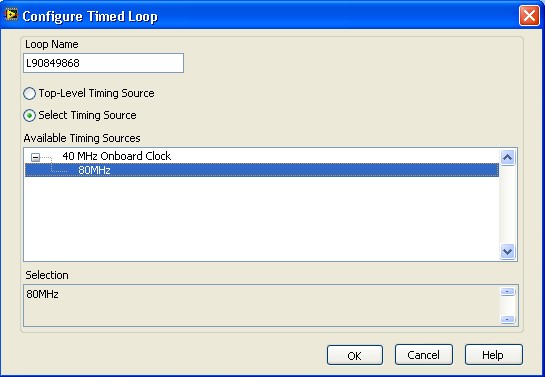

f. Double-Click the SCTL to configure the desired derived clock. Remember the SCTL will execute with a period of 1/2 the derived clock rate.

2. Export Boolean value from Square Wave Generation Express VI

a. Create a SCTL.

b. Place the Square Wave Generator inside. Functions>>FPGA Math & Analysis>>Signal Generation

c. Configure the Express VI to run 'Inside a SCTL.'

d. Create controls for clock specifications.

e. Use FPGA I/O node to write digital channel.

3. Use PWN Generation algorithm to Export Clock

a. Create a SCTL.

b. Place the PWM Out-FPGA SubVI.

c. Wire controls for clock specifiactions.

d. Use FPGA I/O node to write digital channel.

Additional Notes

For additional assistance with specific LabVIEW functions, please use ctrl+h to view the Context Help dialog.

Description-Separate-2

Related Links

Related-Separate-1Related-Separate-2 Patrick Corcoran

Application Engineering Specialist | Control

National Instruments

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.