- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the best way to disable the PWM Output.

09-07-2015 02:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

we use the NI 6602 PCI card to create a PWM output signal. Our application can change the signal period and the and ratio between high and low signal level to create an dynamically PWM signal. But now our problem is to support the case, if the signal ratio is 0 or 100 percent.

In the case of 0 percent, we expect the PWM signal is disabled and the output level is set to 0V.

In the case of 100 percent, we expect the PWM signal is also disabled an the output level is set to 5V.

If we disarm the counter, the output signal level is unspecific.

What is the best way to support these both cases ?

Best regards, Uwe

02-04-2016 09:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Uwe,

I'm sorry that your question has gone unaddressed for so long :-S

Are you still facing this obstacle?

Joe Friedchicken

NI Configuration Based Software Get with your fellow OS users

[ Linux ] [ macOS ]Principal Software Engineer :: Configuration Based Software

Senior Software Engineer :: Multifunction Instruments Applications Group (until May 2018)

Software Engineer :: Measurements RLP Group (until Mar 2014)

Applications Engineer :: High Speed Product Group (until Sep 2008)

02-05-2016 01:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you have a good idea to solve our problem, we take them to be happy. Currently we reprogram the card, but this is very expensive solution in comparison to the normal signal control process. Because we want control the output signal very dynamically.

Best regards, Uwe

02-27-2016 11:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

IT seems trivial, but when you disarm the counter, try to force the digital out to the state you need.

The same signal is sent to the counter to stop it, can be send, with negation or not, to the output/s witha proper logic gate.

cheers,

AL3

---------

02-29-2016 03:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thanks for your feedback, but this is not our problem.

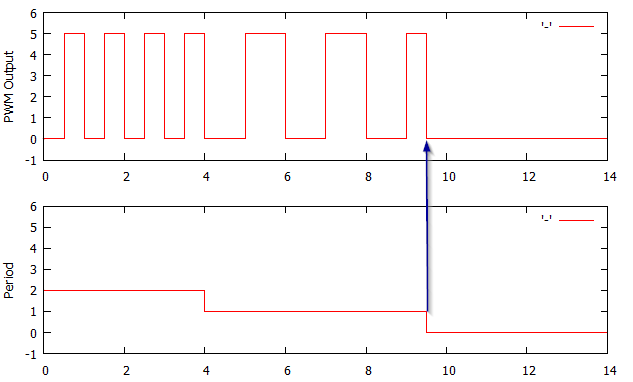

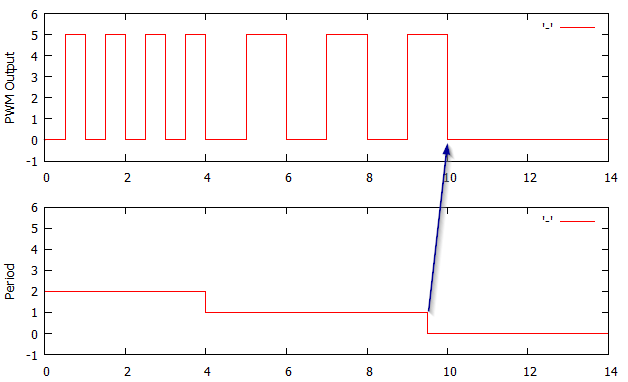

if we disarm the counter at a unspecific timestamp the outputsignal looks like in the following image.

But we wish the Output signal is set to the correct signal level after the current counter value is expired like in the following image.

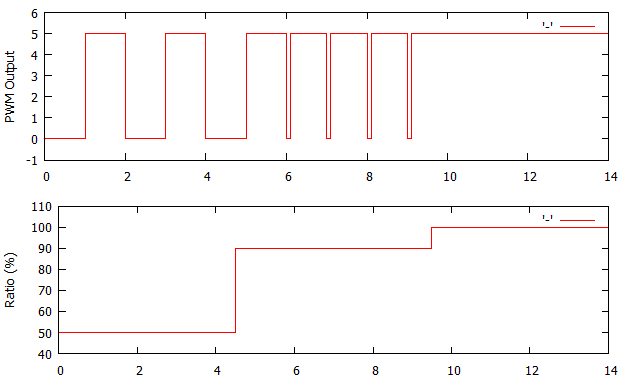

or in Case only the Ratio was changed:

Best regards, Uwe Kerber

03-14-2016 12:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Uwe,

Thank you for providing those images -- the comparison between what you have and what you want is really helpful.

I believe you can achieve the 0 and 100 percent duty cycle scenarios by using interrupts. When generating pulse trains, the counter toggles its output whenever it reaches its Terminal Counter (aka TC) [1]. The 660x devices can assert an interrupt whenever the TC is reached, and by using this hardware event you can disarm the counter at the correct time. When you enable this interrupt, the counter will interrupt every time it toggles, and your interrupt handler must always acknowledge the interrupt, but it should only disarm the counter when it determines that the new duty cycle should be 0 or 100 percent.

In short:

- Use the counter's Interrupt Enable Register to set the G0_TC_Interrupt_Enable field (bit 6 for coutners 0 and 2; bit 9 for counters 1 and 3).

- Acknowlege the interupt every time it asserts by using the counter's Interrupt Acknowledge Register to set the Gi_TC_Interrupt_Ack (bit 14).

[1] NI 660X Register-Level Programmer Manual :: Pulse Generation (page 14)

http://digital.ni.com/manuals.nsf/websearch/4CE1C778F442B01386256C870060F9F3

Joe Friedchicken

NI Configuration Based Software Get with your fellow OS users

[ Linux ] [ macOS ]Principal Software Engineer :: Configuration Based Software

Senior Software Engineer :: Multifunction Instruments Applications Group (until May 2018)

Software Engineer :: Measurements RLP Group (until Mar 2014)

Applications Engineer :: High Speed Product Group (until Sep 2008)

03-17-2016 07:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Joe,

thanks for your answer. I will tryout your idea. The only problem that i see,

is the high interrupt load on high output frequencies. Do you have an idea how

to solve the problem without handling the interrupts ?

Best regards, Uwe Kerber

03-17-2016 10:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

seuwkerb wrote:

The only problem that i see, is the high interrupt load on high output frequencies. Do you have an idea how to solve the problem without handling the interrupts?

Sadly, no, the device cannot aggregate interrupts or be given instructions on how to filter interrupts.

If you're worried about an interrupt storm, then I can only suggest this:

- During normal operation (so duty cycle is 1% to 99%), keep the interrupt disabled.

- When your application needs to set 0% or 100% duty cycle, enable the interrupt.

- Once your interrupt handler is invoked, disarm the counter and disable the interrupt.

Joe Friedchicken

NI Configuration Based Software Get with your fellow OS users

[ Linux ] [ macOS ]Principal Software Engineer :: Configuration Based Software

Senior Software Engineer :: Multifunction Instruments Applications Group (until May 2018)

Software Engineer :: Measurements RLP Group (until Mar 2014)

Applications Engineer :: High Speed Product Group (until Sep 2008)

03-18-2016 02:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Joe,

great idea, i think this is the best solution. I will tryout your idea in the next days.

Thank you for your assistance.

04-26-2016 07:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello joe,

the concept are running but now i have some problems to set the correct output signal.

i used the following code in irq handler to handle the 0% and 100% case.

...

theTIO->G0_Input_Select_Register.setG0_Source_Select( 31 ); /* Low */

theTIO->G0_Input_Select_Register.setG0_Gate_Select( 31 ); /* Low */

theTIO->G0_Input_Select_Register.setG0_Output_Polarity( pol ); /* pol=1 : 5V , pol=0 : 0V */

theTIO->G0_Input_Select_Register.flush();

theTIO->G0_Command_Register.writeG0_Disarm( 1 );

...

But the result ist not solid. DO you have any idea where is the mistake.

Best regards, Uwe Kerber