From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

08-19-2017 06:17 AM

Hello, I have just started using Labview FPGA for a student project and have come across a small problem that I haven't found addressed here already: when I attempt to deploy a VI as a real time application, the source file is either unavailable or the DIO lines disconnect. I am using Labview 2016 and a myRio-1900. I'm not sure if this is a hardware or software question, sorry if this is the wrong place.

I have written a simple code that produce a series of timed pulses used for triggering a MOSFET. Running from the project menu (under the chassis dropdown) the VI runs as desired (outputting pulses to the connector c DIO ports of the myRio). However, I would like to be able deploy the VI as a startup Real Time application, so that I can trigger the MOSFET using the myRio in situ, without access to a computer.

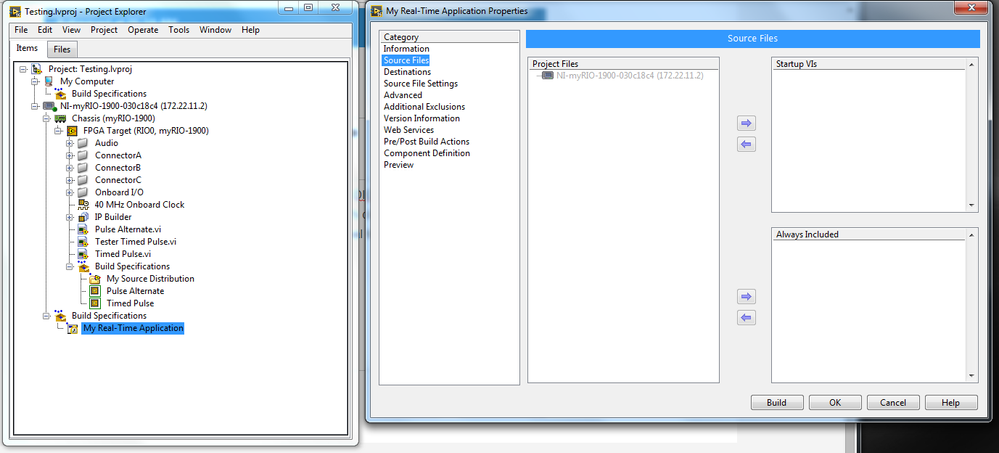

I have looked at the tutorials on the process but they don't appear to come across the issue I've had. If I create a real time application and attempt to build it, the VI is not shown in the source files section (pictured).

Any help would be greatly appreciated.

Thanks,

Max Will

Solved! Go to Solution.

08-19-2017 07:13 AM

Since you have programmed the FPGA, you need to create an interface on your FPGA that your RT can use to control the DIO. I would use a DMA FIFO to send the outputs to the FPGA.

08-19-2017 09:20 AM

Brilliant, I'll look into that. Thanks crossrulz

08-19-2017 09:22 AM

I've also just seen on another forum that the DIO channels on the myRio might be software-timed - so not very deterministic - is that true? Ideally, I'd like to get the pulses down to as near 25 ns apart (a single tick on the myRio's 40 MHz clock) as possible. Would this be an issue using DIO ports?

08-20-2017 06:12 AM

Lookup the specification to make sure, but if controlled by the FPGA, then the DIO can be controlled at the 40MHz rate.