From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

09-02-2016 01:39 PM

Hello,

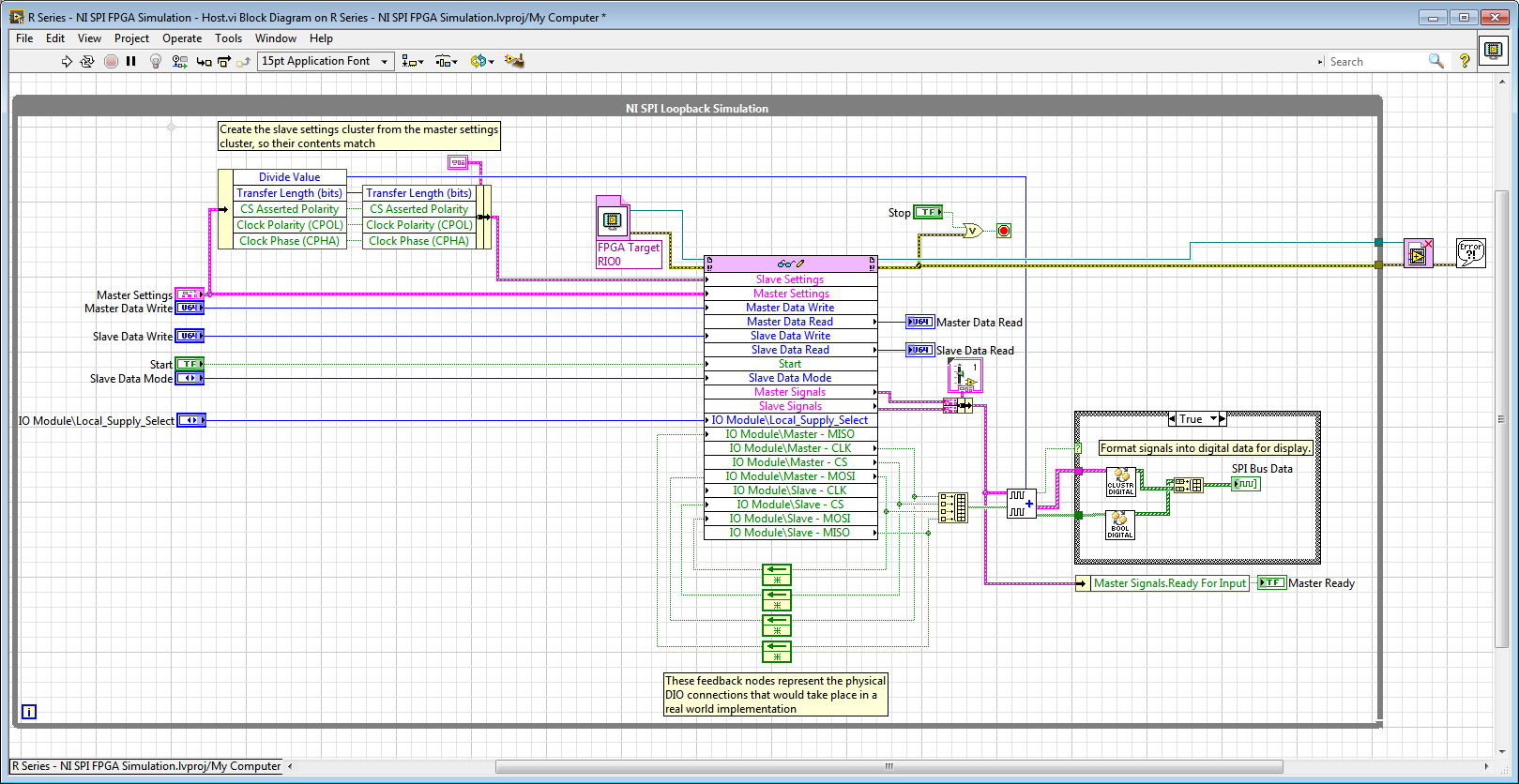

I am trying to run the R Series - NI SPI FPGA Simulation.lvproj project example that comes with NI SPI IP on an actual PXIe-7976R FlexRIO FPGA target with an attached NI 6581B Digital Adapter Module. The example is for a PCIe-7841R but I ported it over to my FPGA target following these steps and made additional modifications to try to make it work with my set-up. I learned that CLIPs for FlexRIO FAMs don't work with Desktop Exection Nodes so I know that I cannot simulate the project as originally intended so I am trying to use FPGA I/O node host side (open FPGA vi reference) to implement on actual hardware.

My first question is regarding my adapter module IO configuration and selection. I've added the IO Module (NI 6581B : NI 6581B Channel) to my project and selected the channels as shown in the table below. I have an actual physical hardware connection as descibed below using two NI SHC68-C68-D4 cables and a break-out board.

I changed the names as well:

I selected these DIO channels because I wanted the DDCA Connector to be the Master and the DDCB Connector to be the Slave. Also, in this CLIP each grouping of eight I/O channels has a write enable signal. I did not use the Port configuration because I needed 4 available DIO channels and I only saw DIO0-3. Is my logic for selecting Channel vs Port correct here?

Following the same strategy as the FlexRIO/NI6581B examples, I modified the FPGA.vi to include some initialization outside of the timed loops:

And in the Host.vi I have a FPGA reference node and have wired the feedback loops accordingly:

When I compile the FPGA and try to run Host.vi LabVIEW inevitably crashes with the Crash Reporter below and and has to restart:

Does anybody know what I am doing wrong here? My guess is that it has something to do with the CLIP/IOModule. Any help is appreciated.

Thank you,

Scott

Solved! Go to Solution.

09-06-2016 06:14 PM

Hi Scott,

I suspect the issue might be related to the fact that your Open FGPA VI Reference node is inside the while loop and trying to open a new FPGA reference with every iteration.

If you move that outside of the while loop, does that resolve the crashing?

Regarding the channel vs. port question, your logic sounds reasonable to me but I would recommend trying it out since that functionality could depend per device.

09-08-2016 03:09 PM

Hi Shalini,

Moving the Open FPGA vi Reference outside of the while loop did indeed resolve the crash problem, and after a bit more research and debug I finally managed to get the example somewhat working. Since this thread is about the crash in particular I will close it.

Thanks,

Scott

12-20-2018 09:42 AM

12-20-2018 09:34 AM

I also have a similar implementation.

The same SPI implementation on NI7961R and its IO adapter module NI6583.

I changed all the things that are required like IO modules and added some more in the FPGA VI like IO Module IO enable all that are required to run in my target and IO module.

The program runs successfully with DIO0(Master -CS), DIO1(Master -CLK), DIO2(Master -MOSI) and DIO3(Master -MISO) and corresponding Slave signal.

In the front panel of the HOST VI what ever I am giving in the Master Write comes in Slave Read and press start. other than that in the SPI Bus Data no changes are reflecting except a few.

Could you please explain me briefly the working of this implementation so that I could continue my thesis This is troubling me a lot.

Also suggest me some other easy ways of SPI implementation using NI7961R and NI6583 if possible.

Thank you in advance.

Best Regards,

Jagan