- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Need urgent help with HSDIO hardware timing

08-13-2012 10:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi everyone,

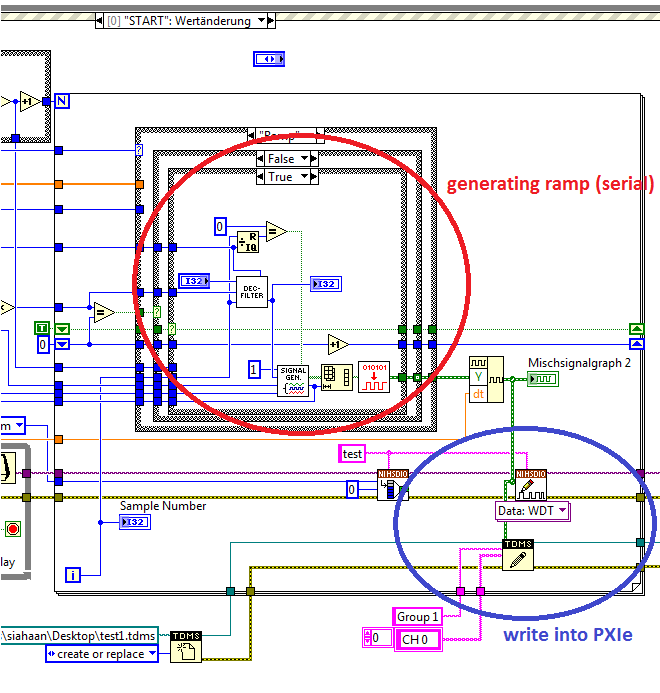

I need urgent help regarding HSDIO hardware timing. I've been working in a project which generating serial ramp using HSDIO pxie device.

I'm using clock rate 40MHz and generating 14 bit of boolean for each step of ramp. And I have to generate simply 256 steps ramp.

Which means, 256 (steps) x 14 (boolean array) x 25 ns (period of 1 boolean value) = 89,6 ns.

What I'm doing right now is with using index of FOR loop as my input data (converting the index into 14bit boolean), then write into pxie device in every iteration,

which means, my data is getting into output in every 1ms time, right? (I'm using windows)

And I want to be able to generate faster than that.

How can I prewrite my 256 steps ramp, then write them all at once into pxie device. I'm really stuck here.

In the picture can you see how I do the write into device in every iteration of FOR Loop.

Regards,

Yan.

08-16-2012 09:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Mystogna,

the fastes loop timing under windows is 1 ms, which we can connect to a timing function,

this only means that the cycle tries to start every ms, the code inside runs faster.

In your case the card runs constant with a clock of 40 MHz and you can only update the

values in a slower rate from the itteration of the loop.

You can use a while loop without timing, then the loop runs as fast as possible,

but the CPU perfomance can get to 100%

Alexander

08-20-2012 11:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi, thanks for responding.

with using example of dynamic generation with script, I can manage to generate the ramp with controllable delay (generate the whole waveform, including delay with script command, then write to the card).

But I still have 1 question, I can test the output of the generation using oscilloscope and cant see the start delay (I'm writing delay at the start, before generating the ramp). My signal generated at 0 sec.

How can I check this start delay? is there any good example delivered with Labview to check this generation? Somehow I cant use the "dynamic generation and acquisition" example to see my generation (cant figure out how to capture the generated signal).

regards,

Yan.

08-21-2012 02:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Yan,

if you want to check if the wait is correct one idee is to set a value before wait to high

and after wait to low, and measure back how long is the high active. You can use a scope

or a DAQ card with counter to do this.

Sorry, i haven´t found an example which do this.

Alexander

08-25-2012 07:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi alex,

somehow I've managed to get the generation and acquisition to work (haven't tried your suggestion, since I might wanna try to generate high for 1 bit, then low, then wait until I start my real generation), do you think it would work?

But anyhow, I would like to save the acquired data with pretty high clock rate (40MHz), how to do that? Oh yeah, to acquire the generated data, I'm modifying a bit the example "Dynamic Acquisition Hardware Pattern Match.vi", which included in Labview.

Do I need to modify the example with while loop (like Fetch Forever example from NISCOPE)? or without the while loop I can save them directly with tdms file. I couldnt find good example with save acquired data with hsdio device.

regards,

Yan.

08-25-2012 10:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi Alex,

I've found the example "Dynamic Acquisition with Fetch.vi". It might help me to fetch the data and save them in a file? I'll try it with the device at monday.

regards,

Yan.