- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA I/O Read/Write Time

04-10-2012 04:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

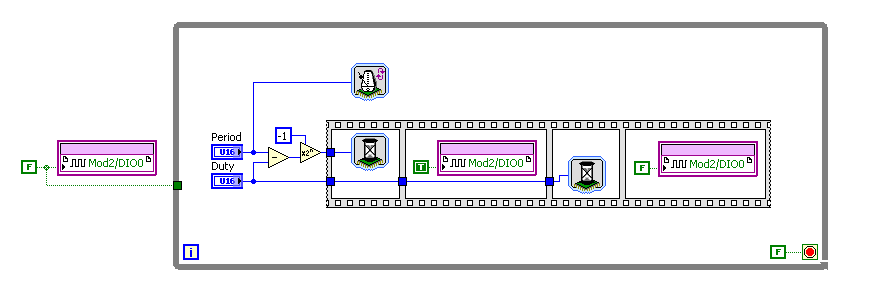

I have a general question about FPGA digital I/O nodes. I am using a cRIO module which does not support SCTL for DIO read/write, so I have placed the read/write in a while loop. My question is how many cycles do these read/write commands take? I can't find this information in any documentation I have searched.

The reason I ask is that I am using a Loop Timer vi to run the while loop at a certain rate, and I am concerned that under certain circumstances when my read/write commands are made near the end of the loop period that they might cause it to run over. Here is a simplified version of my FPGA vi. It is begin used to generate a centered-pulse PWM signal. Thanks.

04-10-2012 08:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You should just benchmark the code. It will be super easy and then you will know for sure.

Certified LabVIEW Architect

Certified TestStand Architect