- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Creating Derived Clocks on a cRIO-9068

01-25-2018 02:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a cRIO-9068 and I am creating a project that is designed to run entirely on the FPGA. I have a base FPGA clock of 40 MHz. I need to create a series of derived clocks (10Hz, 100Hz, 1000Hz and 10,000Hz) each one to drive the polling of a different type of senor plugged into various input modules. However I cannot get to the point of polling the modules as I am unable to perform the most basic task of setting up and creating the clocks that I need to use.

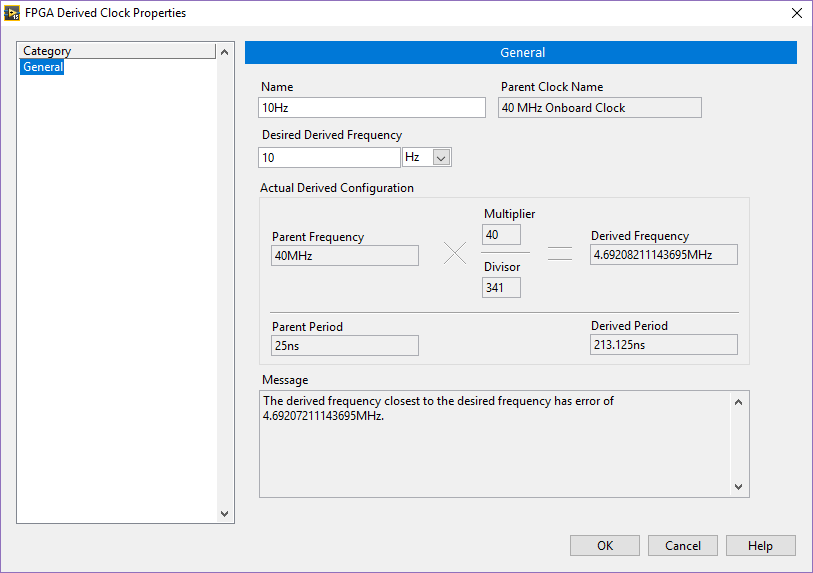

When I try to create a derived clock It won't let me create anything below 4.69 MHz (See image):

Method used: (Chasis -> FPGA Target -> 40 MHz Onboard Clock -> (right click) New FPGA Derrived Clock.

I tried this method to ensure all the clocks would be synchronized.

Thanks,

Mat

01-25-2018 06:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Seems like they are multiples of each other.

Why not make one clock that is the fastest needed and then use a mod function with case structure to have the event run slower?

With a decimate value that is 1 for high speed, 10 for one tenth the rate and so forth.

There are some cases that this will not work for but let's see if this works.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

01-26-2018 08:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For now they are, they will be fixed (not user modifiable once compiled). There are some potential new speeds but they will always be an even number (100 Hz, 200 Hz, etc...)

I would be okay with the approach but as I mentioned I cannot create a clock that is slower than 4.69 MHz. This would mean that I cannot create a 10,000 Hz clock. I think if I can get everything to work my ideal fastest speed would be 25,000 Hz.

I am totally brand new to LabView and so I am not familiar with decimation, could you provide a link that describes how to do this?

01-29-2018 04:21 PM - edited 01-29-2018 04:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yeah you will not be able to derive a clock that slow off of the 40MHz base clock on the cRIO. Instead of deriving multiple clocks within your LabVIEW project, just create simple while loops within your FPGA vi that have the timing set to what you want. After creating this loop just right click the block diagram and select one of the timing functions to control the rate of your loop, such as the wait or loop timer. Then select ms as the unit and make the appropriate conversion from Hz to ms.

Applications Engineering

National Instruments

http://www.ni.com/support

01-29-2018 04:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Would they be synchronized to occur so that overlapping measurements which occur at the same time step happen at "roughly" the same time? Eg I have a 100Hz and 200Hz loop will the measurements for the two loops match up time wise when they are supposed to?

Thanks,

Mat