- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CompactRIO Waveform Library

12-11-2014 02:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I have been trying to add additional module channels to this Project however although I can edit the front panel to change the 'channel info' even though I save the RT VI whenever I open it again it has not saved. I have tried editing the Typedef but the same thing happens. I have added the relevant modules to the FPGA VI and changed the number of channels to 8 and this seems to have compiled OK.

I am relatively new to LabVIEW and have been looking for an example to run both NI-9223 and NI-9237 C-modules and this one seems to fit the bill.

Any guidance would be appreciated.

Many thanks

Bob

12-11-2014 11:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am not sure if I got u right, but: Are you missing a Rightclick onto the Channel Info Frontpanel Control and -> Data Operation -> Make Current Value Default?

12-12-2014 05:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I tried what you suggested however that hasn't worked.

My problems is as follows:

I have amended the FPGA VI to include a DSR module (NI-9237) and an SAR module (NI-9223). The DSR is currently Mod 2 in the chassis (NI 9155) while the NI-9223 is Mod 1. I have associated the FPGA IO node with each of the relevant modules and used separate IO nodes for each type of module and then added the outputs together as recommended in the Application. This VI seems to compile OK though I probably need to tweek the error handling to cover the SAR example as it currently just uses the error handling from the DSR [FPGA] VI.

The main issue is with the front panel of the RT/Host; in particular Areas A and B (see image below):

Currently it shows the 4 channels from Mod 1, however I would like to add the 4 channels from Mod 2.

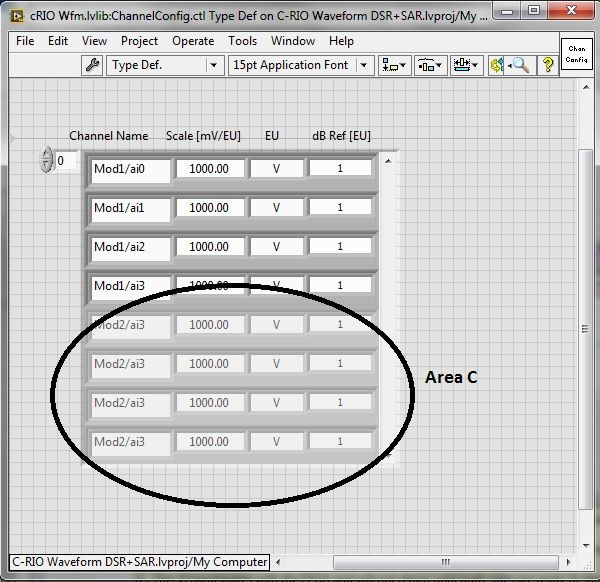

If I change the 'channel config' typedef and 'make current value default' and save the Type Def I get the following:

In this case the last 'current value' has been used for the default even though I changed each of the previous (greyed out) channels to Mod 2/ai0, Mod 2/ai1 etc.

Also as can be seen in Area B in the 1st image, the last 4 items are plot 5, plot 6 etc rather than Mod 2/ai0, Mod 2/ai1 etc.

Any pointers in how I can change this would be much appreciated.

Kind regards

Bob

02-03-2015 01:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Jeff,

First off, your application is awesome and informative! Thanks for your had work.

Have you revisited the idea of adding analog waveform output functionality to the cRIO Waveform Library? My applications require simultaneous AI-AO. I have successfully implemented the shipping example "Multi-function synch AI-AO" or something like that for DAQmx. I have a need to duplicate this capability with cRIO and I wanted to check in with you to see if you are on the fence about adopting this functionality.

Also, do you have more documents similar to the "Customizing the FPGA VIs.pdf" that is included in the Example cRIO Waveform Project? This one has proved helpful in gaining a grasp of RT-FPGA programming structure.

02-26-2015 06:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

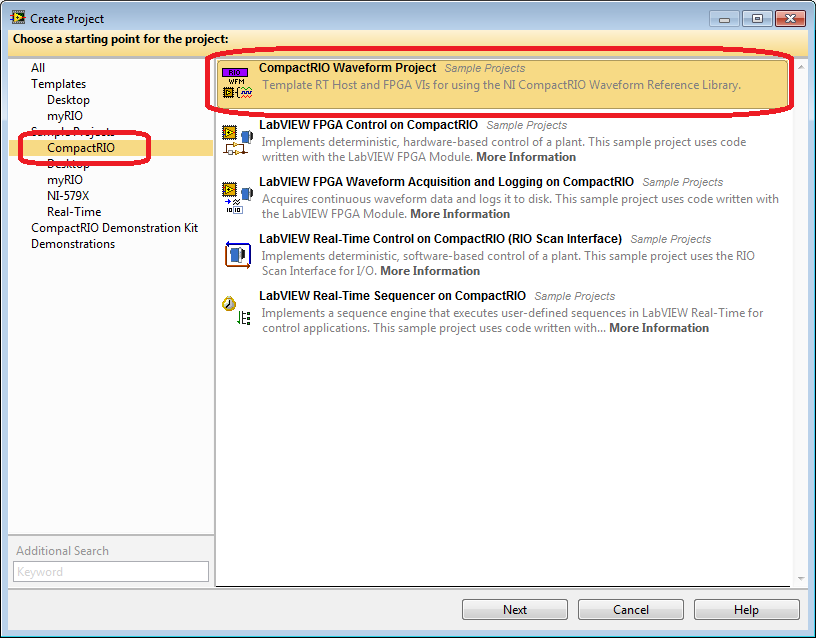

for some reason, I am missing the example projects that I see in the description. Anyone an idea?

I use Labview2013, installed the package with the package manager without any issues.

Thank you.

02-26-2015 11:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

03-06-2015 05:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I am trying to get my NI9237 (Analog Delta Sig Half Bridge Strain) to read continuously using the cRIO Waveform Reference Application, specifically using the RT Cont Acq VI that you used. I get a similar timeout error that you mention in your FPGA Part item 3) and wondered how you solved it. I have tried increasing the timeout to the DMA and changing it to -1 but get the same error.

I realise it is nearly two year ago when you posted your reply but would be grateful for any advice.

Kind regards

Bob

03-06-2015 05:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

My recent post refers to SEGIO's post of 04-11-2013 10:29 AM

Bob

08-17-2015 07:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Tring to add Temperature (9211) module to FPGA. Getting underflow error on the RT vi. Does the loop for 9211 look ok?

08-26-2015 09:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can I also see how you are configuring, starting and stopping the 9211? It is a Delta Sigma module so it needs explicit sample rate, start and stop commands.