- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Sync Trigger Generation Problem in multiple USRP RIO 2943R synchronization problem

Solved!07-18-2016 05:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sync Trigger Generation Problem in multiple USRP RIO 2943R synchronization problem.

From previous SR you may already know that I am stacked in the multiple USRP RIO synchronization problem, especially in the signal-based mode. Now, I can narrow down the problem is mainly because of the sync trigger signal generation.

First of all, I have read the artcle and discussion in the following two links:

http://forums.ni.com/t5/USRP-Software-Radio/how-to-synchronize-multiple-usrp-rio-294x-devices/td-p/3...

http://zone.ni.com/reference/en-XX/help/373380D-01/usrphelp/synchronization/

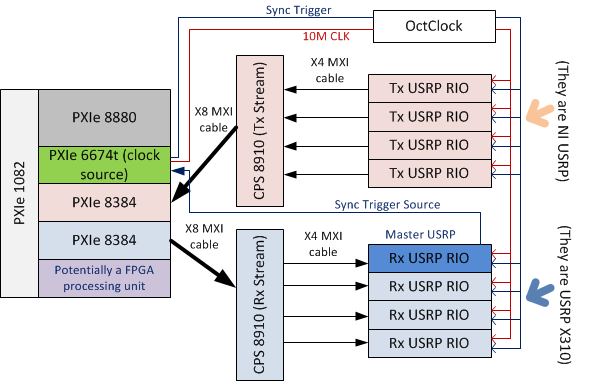

and I made my hardware connection according to the suggestions in the second link. My system schematic is shown in the following picture:

I verified the connections of OctColck and PXIe 6674T. They are all connected correctly and the cable are well functioned. I am using the niUsrpRio200_XcvrSyncPps.lvbitx.

According to the description in the documents and forum discussion, the 1st USRP RIO in the device list will be considered as the Master USRP. Then, the FPGA in master USRP RIO will output "sync trigger" signal via "PPS Trigger Out" SMA port in USRP RIO box.

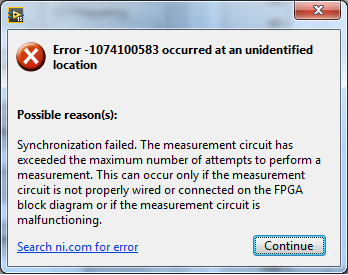

Based on the my testing of the system, the first impression I have is the Master USRP does not output "sync trigger" properly. The host VI reports the error like this:

I was trying measure the "sync trigger" by using oscilloscope, but I found it is impossible, as the host VI cannot even run, so, there is no signal can be seen from the "PPS Trigger OUT" port.

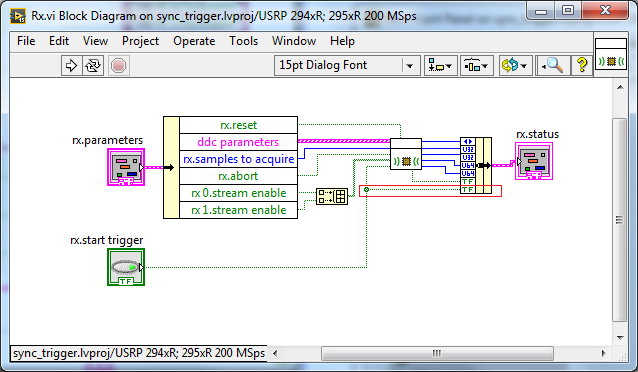

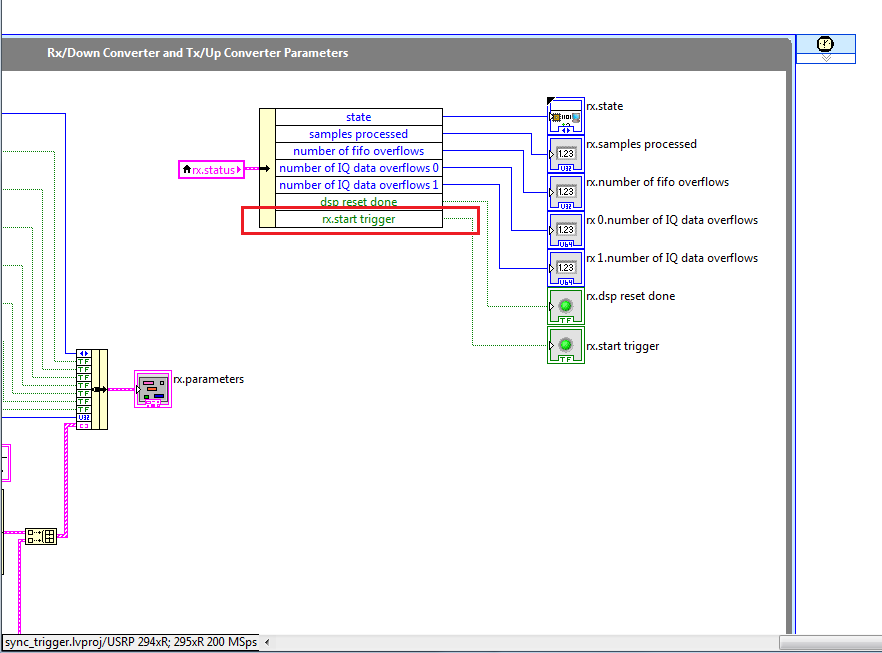

Then, I think whether I can observe this "sync trigger" signal in host VI by import this signal from FPGA to host VI. I made some modification on FPGA VI as shown in following picture in order to observe this signal from host VI front panel. but not so successful. the rx.start trigger and tx.start tragger do not appear on the Host vi Read/Write Control Function.

Solved! Go to Solution.

07-18-2016 08:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

How is you 6674T configured? It's the one piece of hardware that needs extra configuration before the Sample Project will work.

07-18-2016 09:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brook, Thanks for reply.

My 6674T work in follwing the steps as blow:

1. Generate 10M hz ref clk from 6674T, connects to OctClock 10M Ref in.

2. Route "sync trigger" from PFI2 (in) to PFI4 (out). PFI 4 connects to the OctClock PPS in.

I've tested the connectivity of the 6674T ports and OctClock ports. They are all will connected and cables are good, and with exactly same lenght.

07-18-2016 09:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Gotcha.

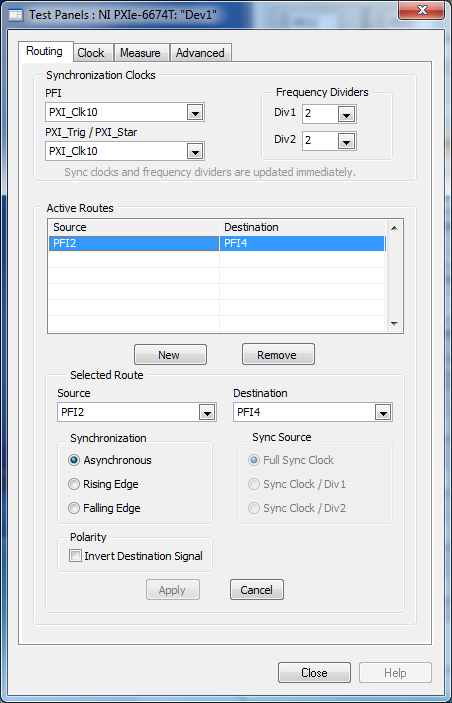

As per my reply here, you likely need to adjust (lower) the 6674T's threshold for PFI2 (the input port) if you haven't already. Can you confirm you've already done this? A screenshot of your 6674T configuration code or 6674T test panel would be helpful. Here's my 6674T configuration:

Routing:

Advanced:

07-18-2016 10:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brooks,

Thanks for the reminding the driving voltage problem. I have not done this, I will make change soon and test.

However, I do not think it is the main problem as with current set up, I can route the signal from PFI 2 to PFI 4 successfully. For testing I use one USRP to generate a PPS signal (not sync trigger, though they are suing same SMA port), route it via 6674T, and test 8 OctClock output. I can measure perfect pulse per second.

Anyway, I will make the change and test again, to see is there any progress, will update once I get the result.

Cheers,

Bo

07-18-2016 11:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brook,

I made the change on 6674T according to your suggestion as blow: (but is still shows the same synchronization error)

07-18-2016 11:34 AM - edited 07-18-2016 11:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can you post a screenshot of the 6674T's routing configuration too?

07-18-2016 11:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here is the 6674T routing:

07-18-2016 11:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Gotcha.

Can you confirm your OctoClock switch is set to External and the External LED is lit too?

07-18-2016 12:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Of course. External source for OctClock, LED is on.

Actually, I've used this setting for "time-based" sychronization receiving, and it works well. It distribute the 10MHz clk and standard PPS signal well.

The problem happened when I try to use "signal based" sync.

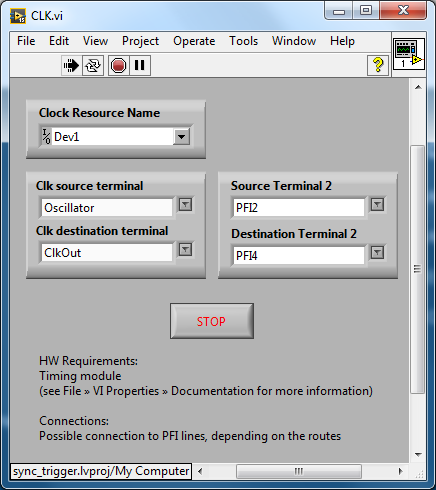

One small question: after the setting of 6674T from NI MAX, do I need to run the CLK generating and stigger routing VI for 6674T like below?